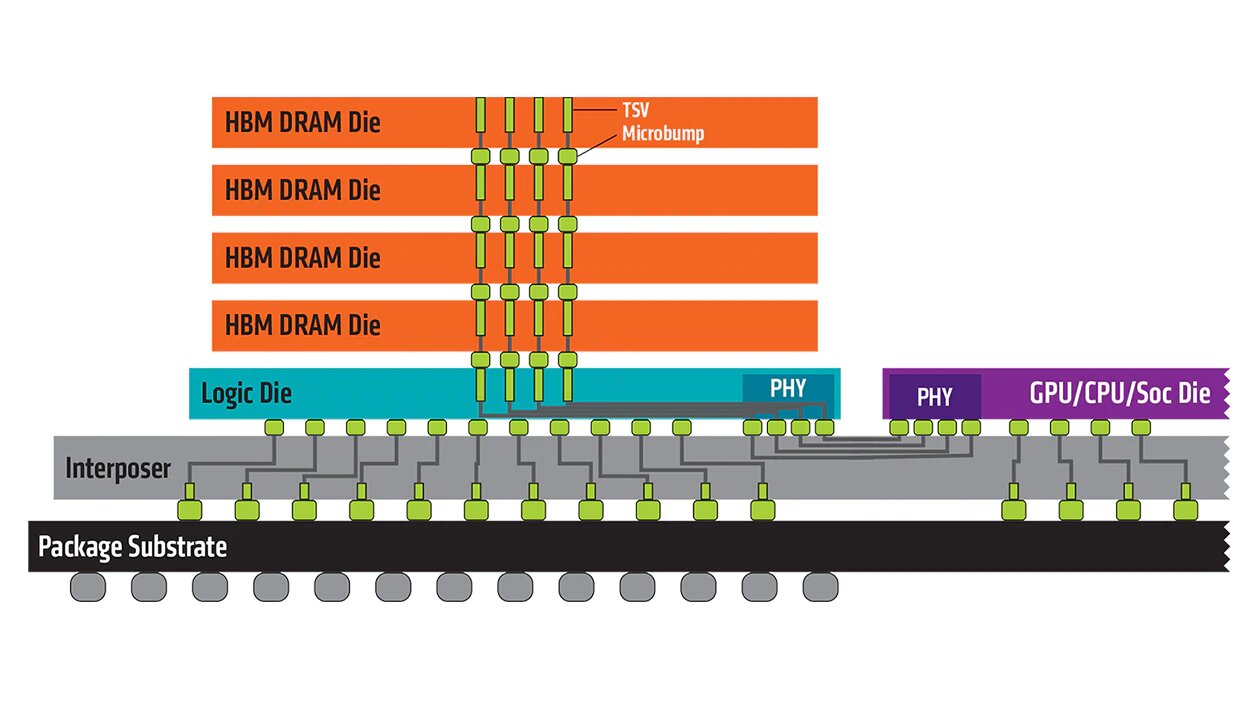

Jahrelang war HBM3 auf den Roadmaps von Rambus, zuletzt aber verschwunden. Nun wird es dank Mitbewerbern wiederentdeckt, denn SK Hynix ging kürzlich in die mediale Offensive und zeigte erste mögliche technische Daten. Diese will Rambus weit überbieten.

Lange diskutiert und noch nicht fertig

Bereits vor fünf Jahren nahm ComputerBase im Rahmen von Hot Chips 28 an einer Veranstaltung von SK Hynix und Samsung teil, die sich unter anderem mit HBM3 befasst hat. Seinerzeit waren 512 GB/s Bandbreite für HBM3 im Gespräch, was vor fünf Jahren eine große Nummer war. In fünf Jahren ist jedoch viel passiert, von HBM2 ging es nicht direkt zu HBM3, HBM2e übernahm als Zwischenschritt. Und von den Roadmaps aus Jahr 2018, die HBM3 im Jahr 2020 sahen, ist mehr als ein Bild nicht geblieben.

665 GB/s Bandbreite „und mehr“ gab SK Hynix für den Einsteig des neuen HBM3 kürzlich an, der Takt würde demnach bei 5,2 Gbit/s liegen. Rambus will das übertreffen und 1,075 TByte pro Sekunde Bandbreite liefern, das sind 8,4 Gbit/s an Takt. Das wäre auf dem Papier dann mehr als eine Verdoppelung von aktuellem HBM2e, der im Maximum mit 460 GB/s beziffert ist. Dass es auch nach unten gehen darf, erklärt Rambus mit der Unterstützung für Taktraten von 4,8, 5,6 und 6,4 Gbit/s.

Das Problem daran ist aber, dass Rambus nur bestimmte Controller und Funktionen bereitstellt, den Speicher am Ende nicht selbst entwickelt. Das bleibt immer noch Aufgabe der DRAM-Produzenten, ein HBM3-Chip direkt mit dem Maximum der Spezifikation ist deshalb erst einmal unwahrscheinlich, weshalb die Herangehensweise von SK Hynix vermutlich mehr der Realität in den ersten Jahren entspricht.

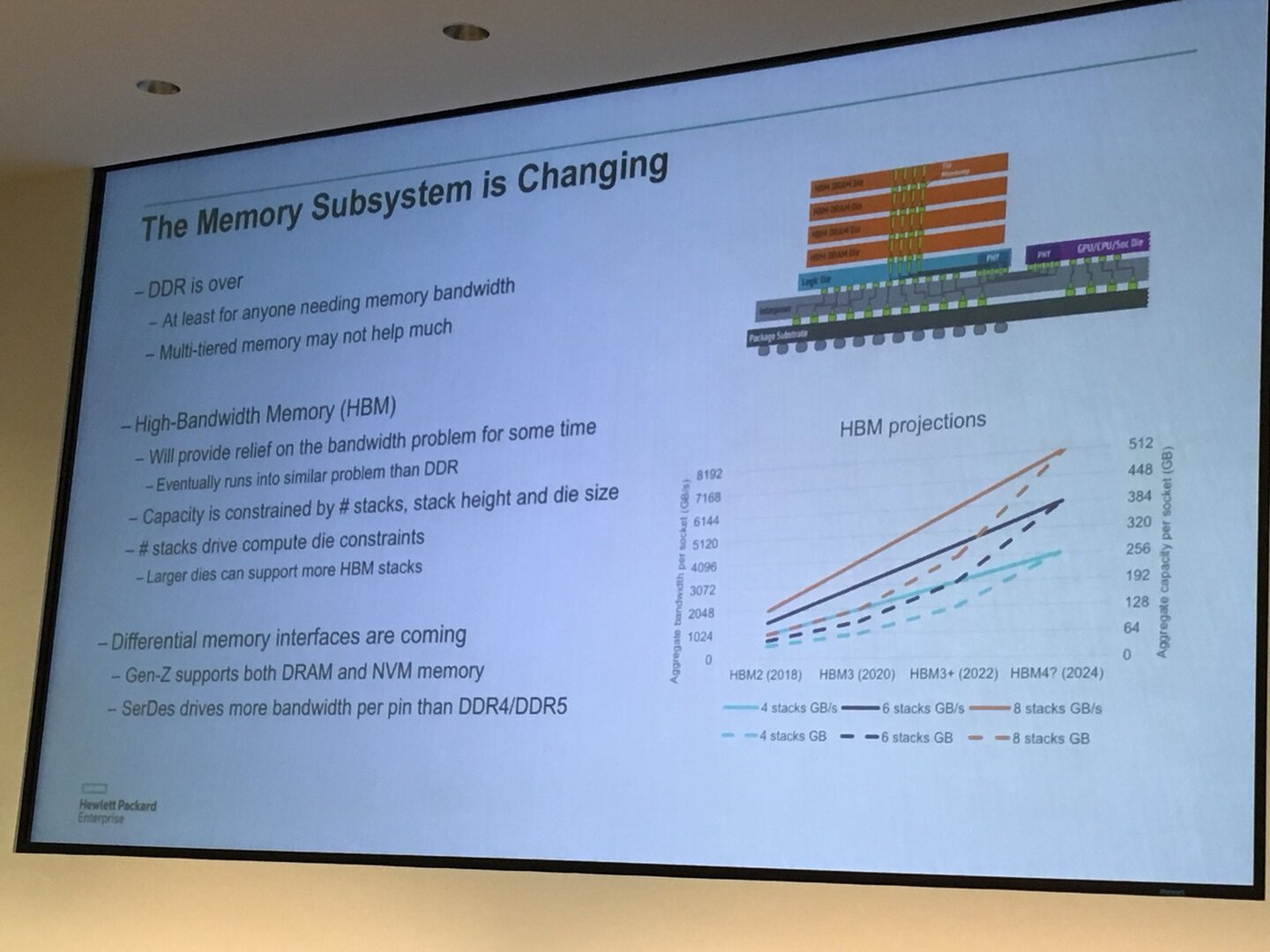

HBM im Aufbau (Bild: AMD)

HBM im Aufbau (Bild: AMD) Bis zu 64 GByte pro Stapel

Am Aufbau von HMB3 wird sich im Vergleich zu bisherigem HBM2 und HBM nichts ändern. Rambus spricht weiterhin von der Nutzung eines 2,5D-Interposers, die eigentlichen Speicherchips werden zusammen mit Phys auf einem Interposer gestapelt. Wie hoch die Speicherkapazität sein wird, ist noch nicht bekannt. HBM2e erreicht mit 12-fachem Stapel an Speicherchips aktuell bis zu 24 GByte, bei HBM3 werden, wie von Rambus heute bestätigt, erstmals 16-fache Stapel in Spiel kommen, sodass zumindest direkt 32 GByte bereitstehen würden. Auf lange Sicht werden 64 GByte angestrebt.

Wann das soweit sein wird, steht ebenfalls noch in den Sternen, eventuell ist 2022 eine erste Lösung zu sehen, doch wenn die Vergangenheit eines gelehrt hat: Bei HBM dauert es immer noch etwas länger. 2023 oder 2024 dürften weitaus realistischer sein.

HBM3-Memory-Subsystem (Bild: Rambus)

HBM3-Memory-Subsystem (Bild: Rambus)