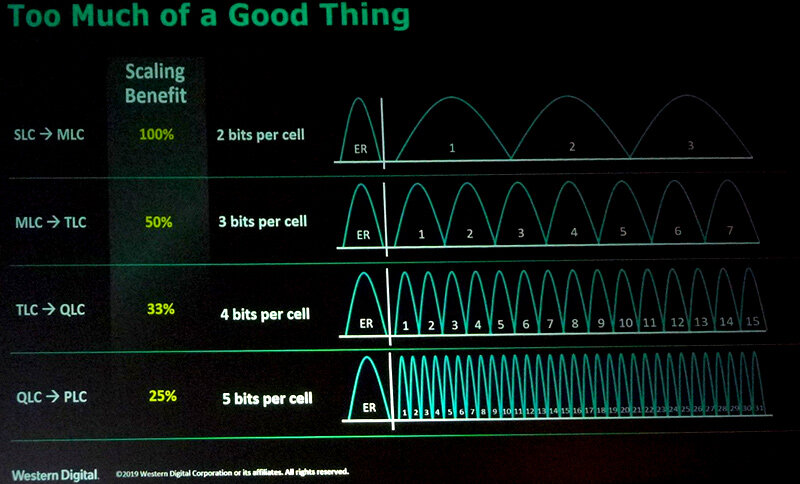

While NAND-Flash has meanwhile reached four bits per memory cell (QLC), there are already considerations for the next step: With Penta-Level Cell (PLC) five bits per cell are saved. However, the technology is not yet ready for the market. The head of technology at Western Digital does not expect this before 2026 either.

PLC for first segments only after 2025

At the Bank of America Merrill Lynch 2021 Global Technology Conference, Siva Sivaram, President, Technology & amp; Strategy at Western Digital, also answered questions about upcoming technologies such as PLC-NAND. In his opinion, the changeover from QLC to PLC will be a few years away. Only in the second half of the current decade, ie not before the year 2026, does Sivam expect “that some segments will begin to receive 5 bits per cell”.

So I expect that transition will be lower – slower, so maybe in the second half of this decade we are going to see some segments starting to get 5 bits per cell.

Siva Sivaram, President, Technology & amp; Strategy Western Digital

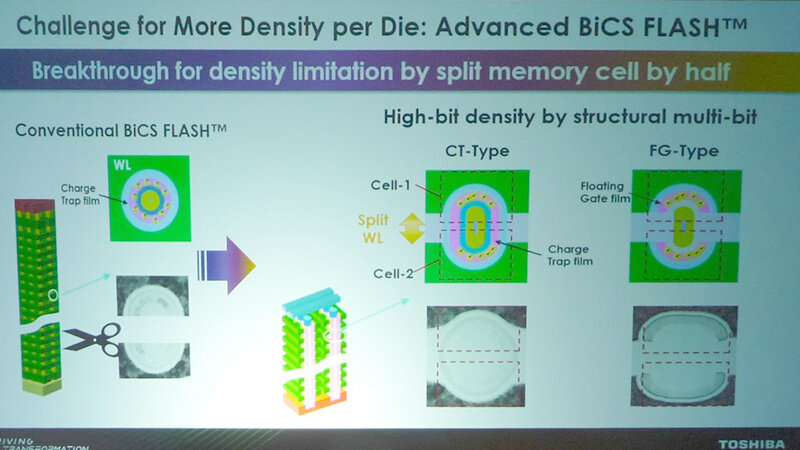

The first publicly announced but also cautious considerations on PLC-NAND with 5 bits on the part of the flash partners Kioxia and Western Digital already took place at the Flash Memory Summit 2019. The memory cell structure for 3D-NAND with smaller cells and potentially more bits per cell, known as “Twin BiCS Flash”, was later presented as a possible pioneer for PLC. Intel also has PLC-NAND on its list and is very confident that its own floating gate architecture is better suited to this than the competition's charge trap flash technology. Since Intel's NAND division will soon be taken over by SK Hynix, it remains to be seen how the new owner thinks about it.

-

” Halved “memory cells for double the data density? (Image: via PC Watch)

” Halved “memory cells for double the data density? (Image: via PC Watch)

Image 1 of 3

“Halved” memory cells for double the data density?

“Halved” memory cells for double the data density?  Partner Western Digital also has PLC-NAND on the slip

Partner Western Digital also has PLC-NAND on the slip As with the change from SLC (1 bit) to MLC (2 bit), then to today's widespread TLC (3 bit) and now, occasionally, QLC (4 bit), the progress in storage capacity also means disadvantages. For storing 5 bits, a distinction must be made between 32 states in the cell. The storage process is therefore much more complex and error-prone than with QLC-NAND. The more voltage levels have to be differentiated, the more the controller or the engines have to do to correct errors. With each additional bit, the window for reading out the information and, analogously, the shelf life is potentially decreasing.

“A lot is sacrificed” for 25% more capacity

Western Digital is the subject of PLC so far cautiously. The increase in storage capacity from QLC to PLC is only 25 percent, which is even less than when moving from TLC to QLC. Ultimately, it remains to be seen whether it is worthwhile to accept the disadvantages. “You have to sacrifice a lot to make this profit,” said Sivaram.

To get that gain you're sacrificing a lot, you need additional redundancy, additional ECC; so the net gain supposed to the performance loss may not be quite as desirable.

Siva Sivaram, President, Technology & amp; Strategy Western Digital

QLC is growing slowly, the weakness remains

When From public announcements in 2015, QLC-NAND didn't take that long before manufacturers presented the first QLC-NAND in 2018. The first consumer SSD with QLC was the Intel SSD 660p with the QLC memory that was developed jointly with Micron at the time.

The editors recently announced the Intel SSD 670p ( Test) tested a successor. The performance of the new QLC generation has improved significantly, but large write transfers beyond the SLC cache remain QLC's Achilles heel. With PLC, the writing weakness could be even stronger, which would limit the possible areas of application, but would be conceivable for archiving purposes, as was also intended for QLC at the time.