Intel has brought nine presentations to this year's IEDM research conference. They show parts of a possible future of the industry for the next 10 years. As usual, exact assumptions are rare, but parts of the research will be combined with others to eventually actually be found in products.

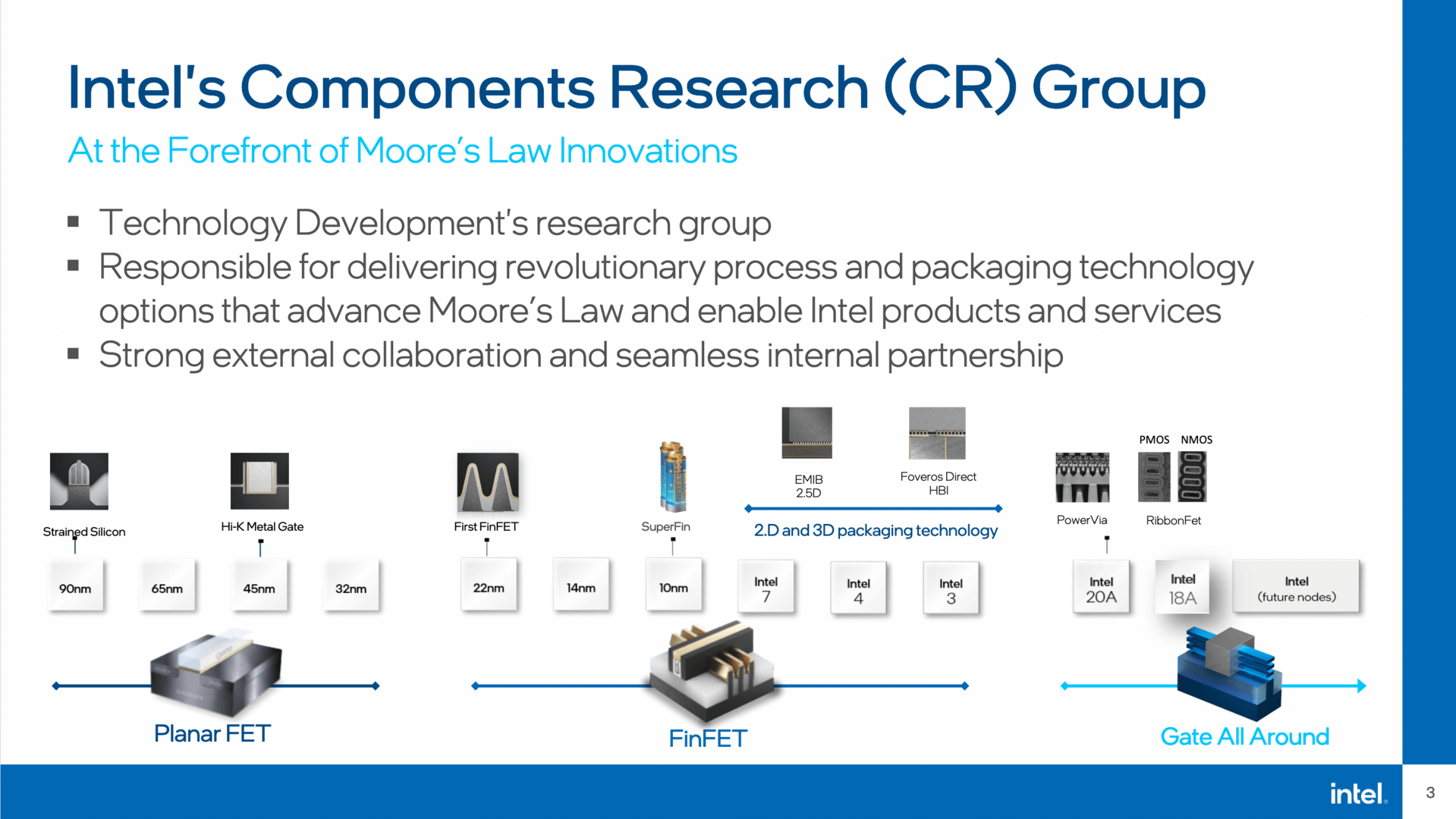

And so Intel makes it clear right from the start that these are not product announcements, but considerations for the next five to ten years, how current problems can be tackled or how one can simply imagine a coming generation. After last year, Intel's Components Research Group (CR) likes to emphasize again what successes it has contributed not only for Intel but for the entire industry in the past and what is to come in the near future.

Intel's achievements over the past few decades (Image: Intel)

Intel's achievements over the past few decades (Image: Intel)Packaging is one of the current topics and will remain so in the near and distant future. With Ponte Vecchio, Intel has recently presented one of the most extreme possibilities and is now making it commercially available, but more obvious solutions are the order of the day. The already well-known hybrid bonding has recently made great strides at Intel, according to their information. A year ago 10 microns (micrometers) were the order of the day, at this point three microns are now the order of the day. Within a year, Intel speaks of a 10-fold improvement in the interconnect connection in terms of performance and power consumption.

And that's not the end of it, Intel believes that you can advance from the micrometer to the nanometer range without any major difficulties. “Several hundred nanometers” (1 micrometer = 1,000 nanometers) are the target for the next few years, one researcher explained when asked.

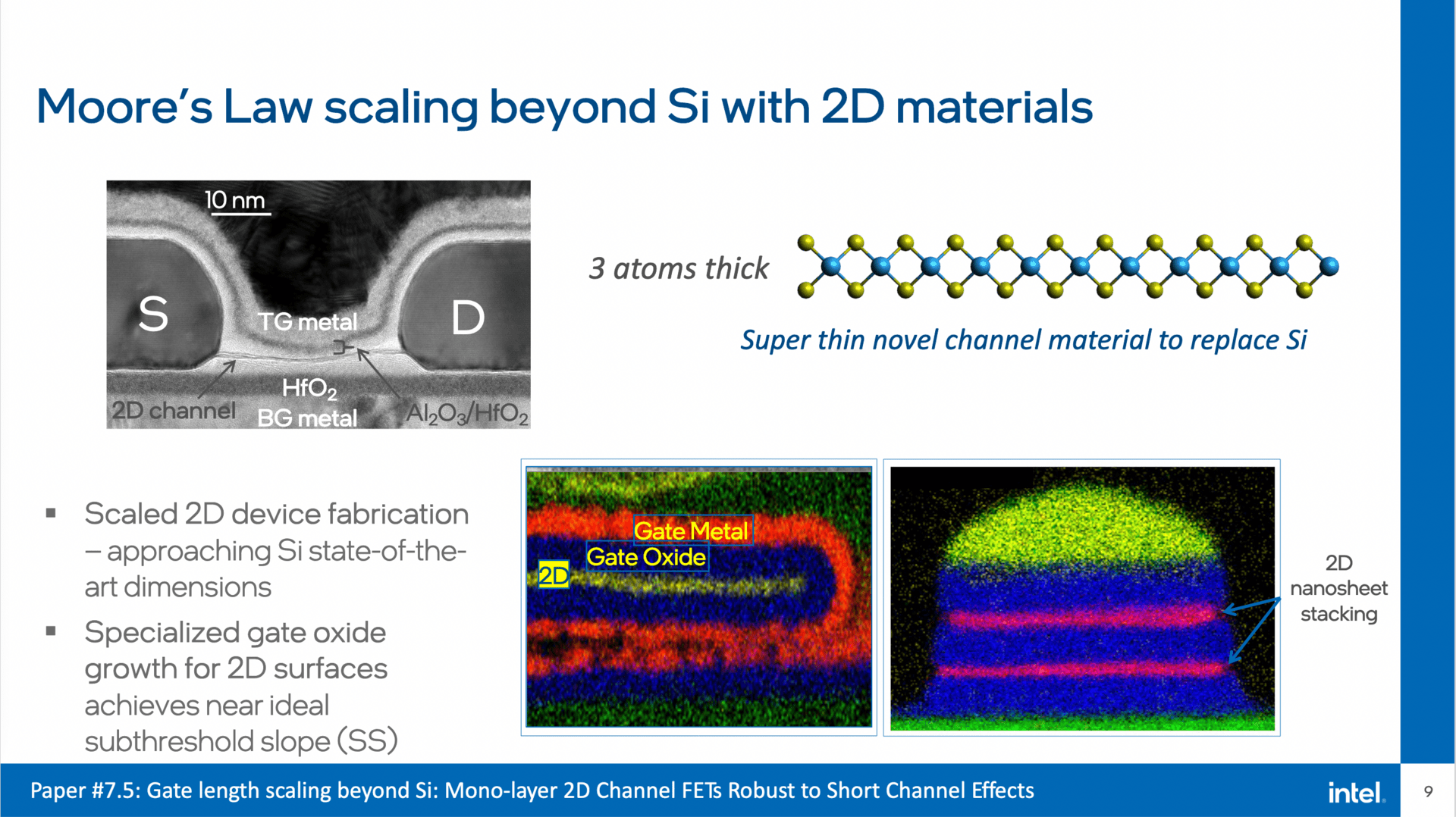

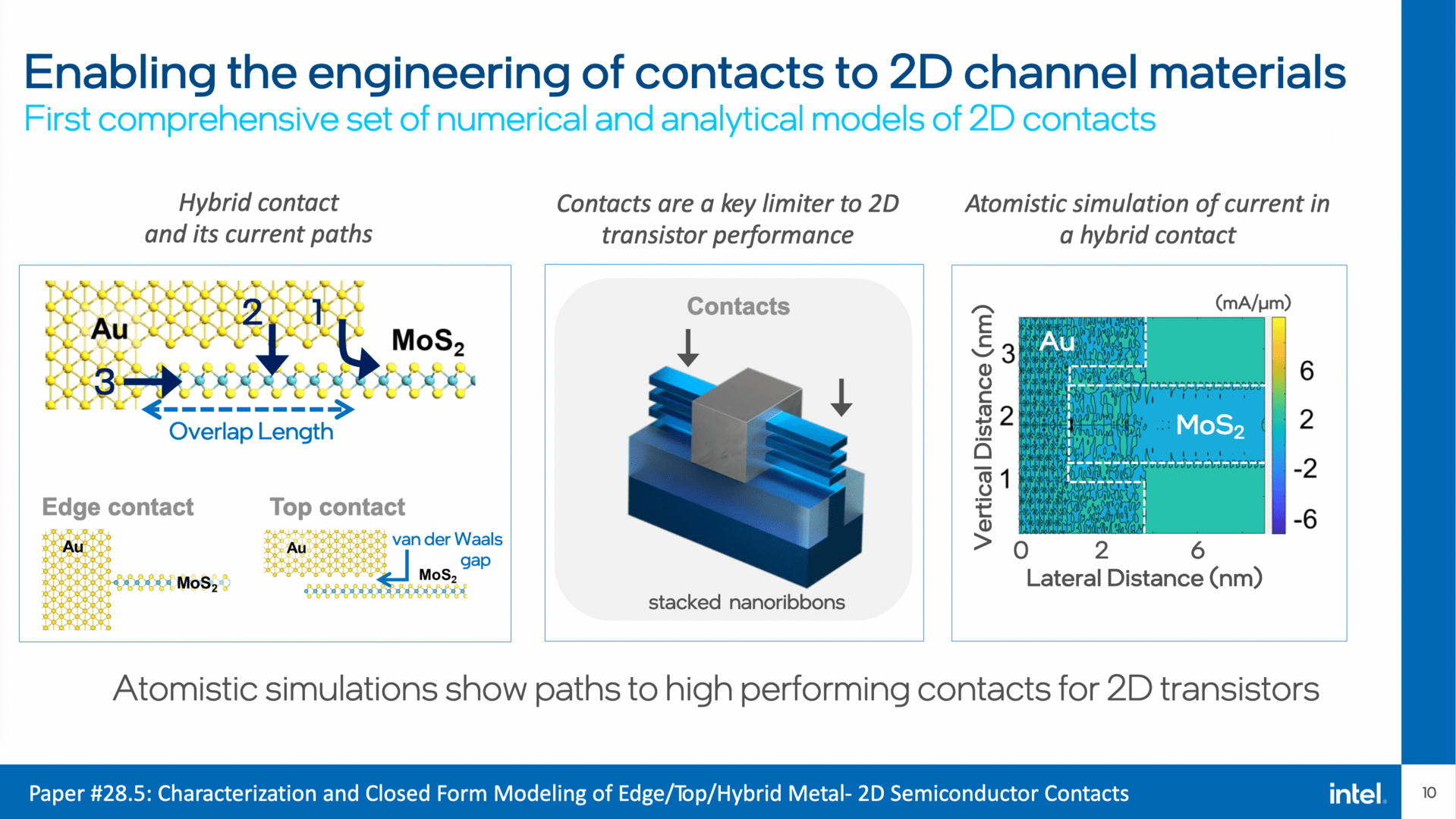

New materials should also help. Super thin materials are slowly coming into the 2D area, they could circumvent many problems of current materials. But first of all this has to succeed, with the help of many small steps and new model tests, the researchers are gradually getting closer.

-

2D materials at a glance (image: Intel)

2D materials at a glance (image: Intel)

Image 1 of 2

2D materials in view (image: Intel)

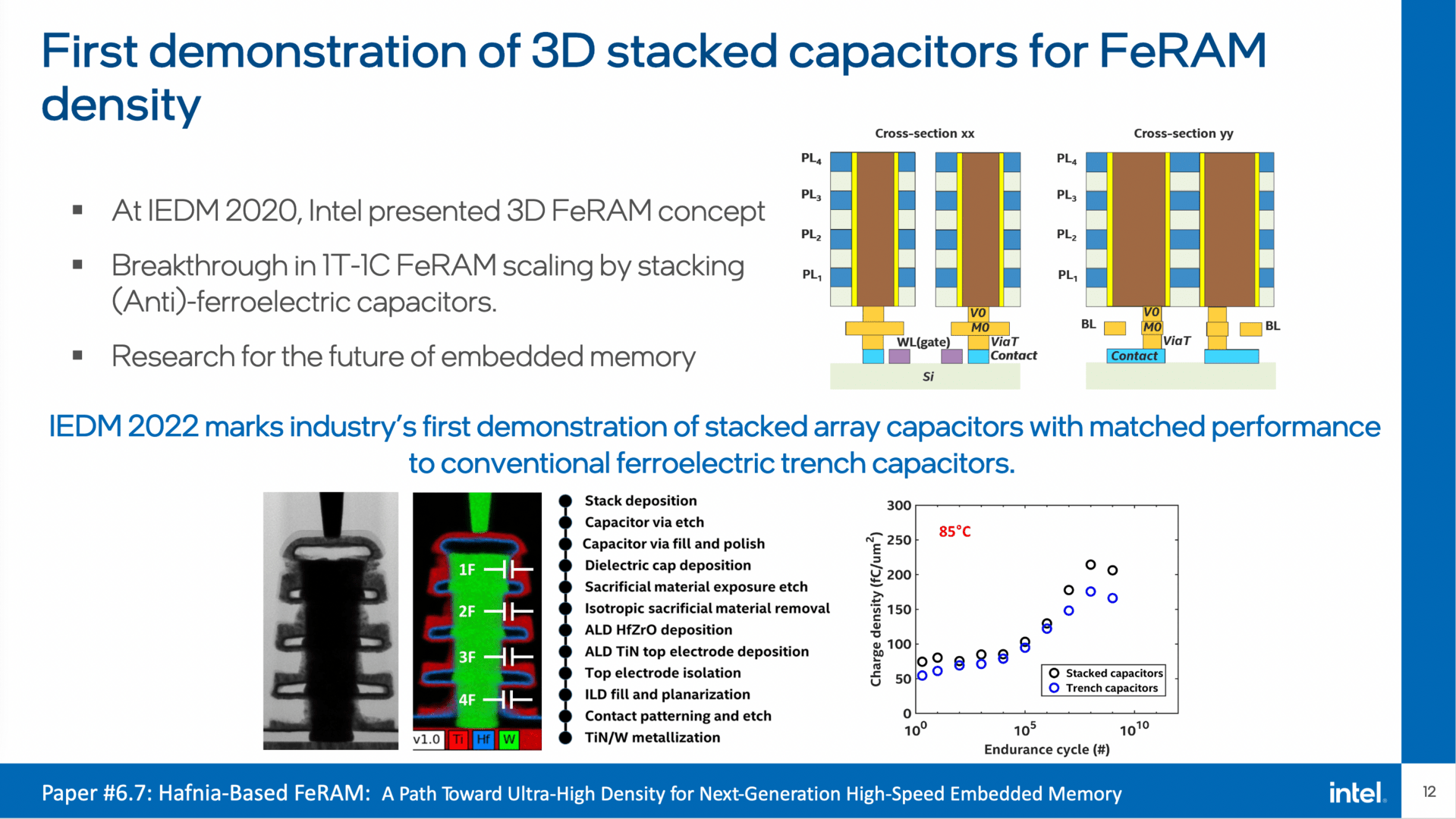

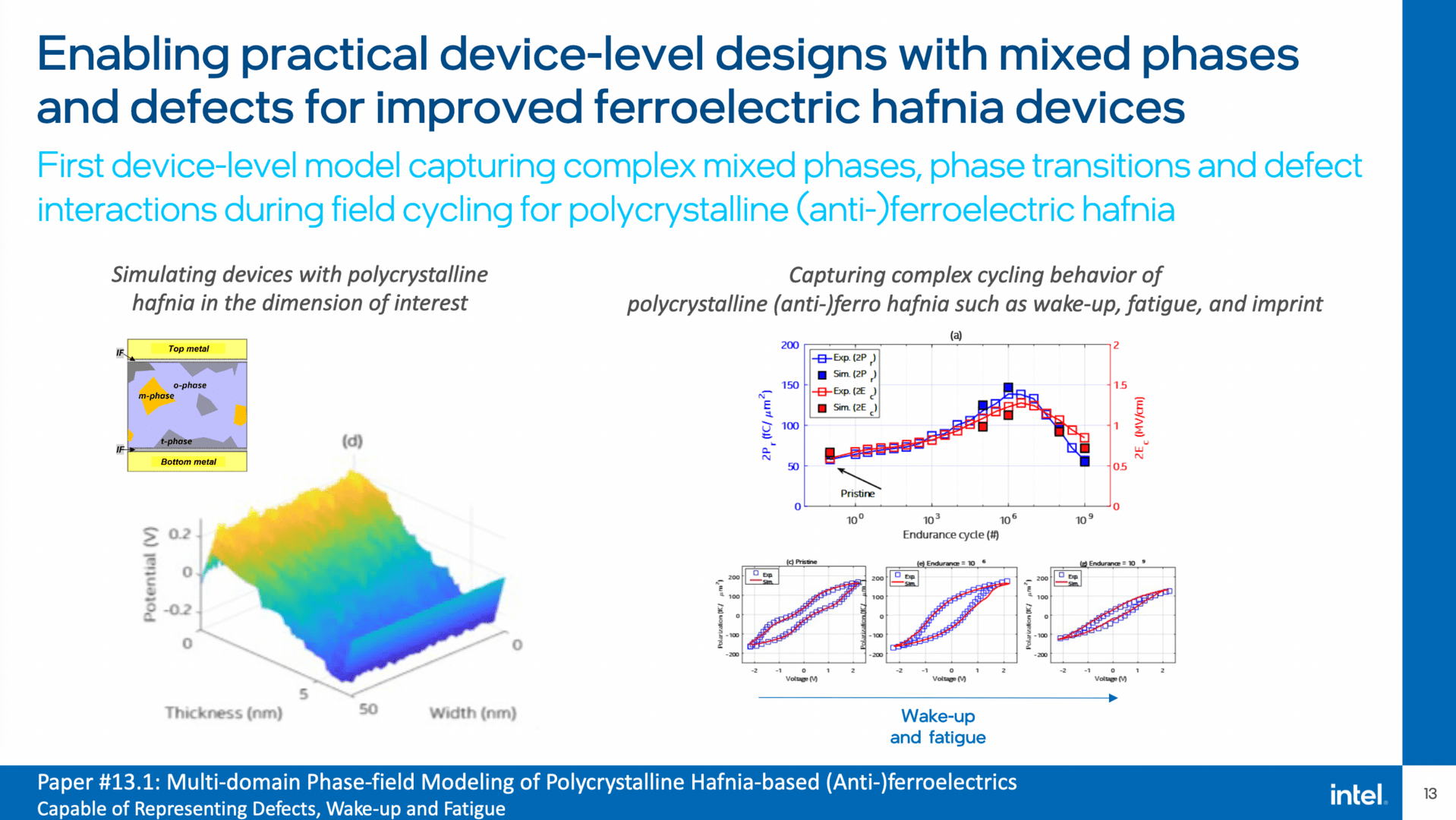

2D materials in view (image: Intel)Intel is not only researching in these areas, but also in alternatives to SRAM and RAM. FeRAM could be such a solution, it would be primarily intended for embedded memory. After many years of wishful thinking about a snappy memory that could sit somewhere between DRAM and SRAM, e.g. as a cache, Intel shows functional FeRAM stacked high.

-

FeRAM as a possible new memory (Image: Intel)

FeRAM as a possible new memory (Image: Intel)

Image 1 of 2

FeRAM as a possible new memory (image: Intel)

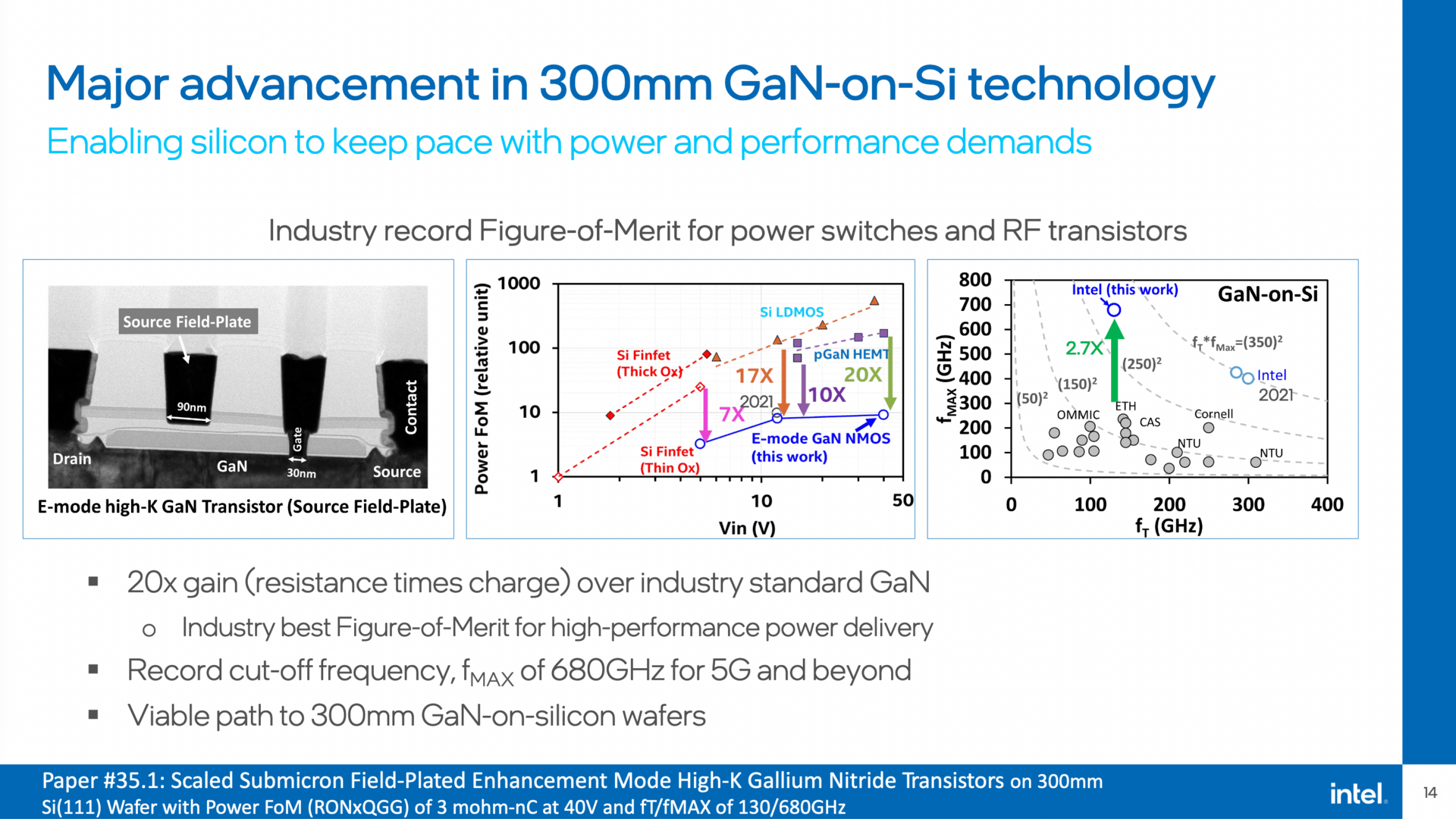

FeRAM as a possible new memory (image: Intel)Intel is also not letting go of the topic of GaN silicon wafers, although they themselves do not currently use it in their production – but possibly via their foundry division. So far, GaN (gallium nitride) wafers have been manufactured in sizes of six or eight inches, the problems of scaling it to 300 mm (12 inches) have been too great. Intel intends to take this a step further this year and is hoping for rapid implementation in the coming years. Because the market for the extremely low-loss but very powerful semiconductor chips is booming, capacities are being expanded on a large scale, such as at Infineon.

300mm GaN-on-Si wafer within reach (Image: Intel)

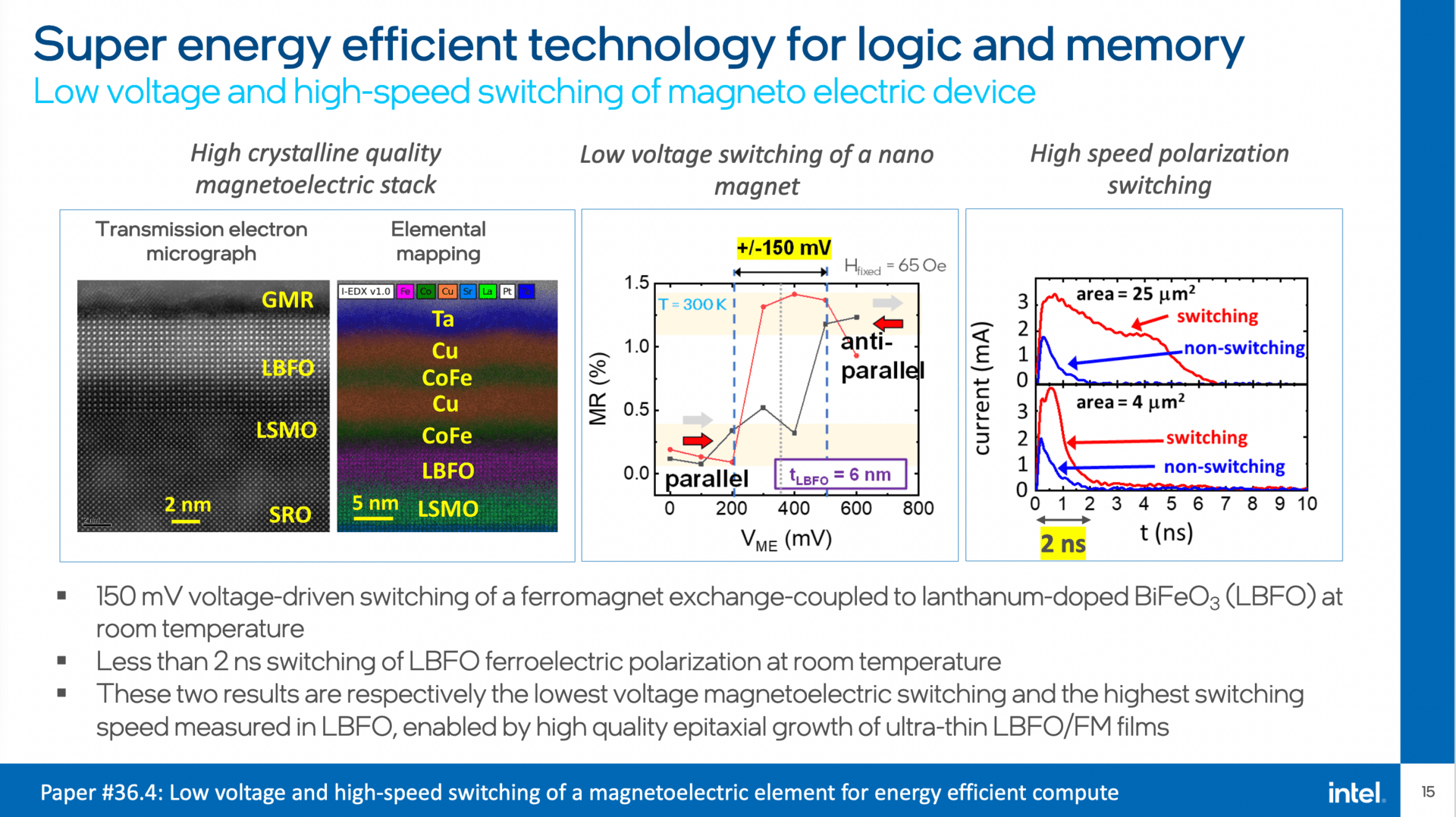

300mm GaN-on-Si wafer within reach (Image: Intel)And last but not least, Intel hasn't forgotten to look at energy saving. For technical reasons, most chips today only work down to around 0.6 volts. A current research project shows possible adjustments in this area, so that it could go down to 0.15 volts in the future. This, in turn, could enable a whole new class of low-power devices.

0.15 volts instead of the previous 0.6 volts as the new minimum (Image: Intel)

0.15 volts instead of the previous 0.6 volts as the new minimum (Image: Intel)Intel is ultimately just one of many companies presenting their research. The entire program comprises 55 pages (PDF document), which will be presented over four days. At the beginning of the new year, parts of these will also be published.

ComputerBase has received information about this article from Intel under NDA. The only requirement was the earliest possible publication date.