While the rumor mill recently reported several times a week about allegedly new, often heavily modified specifications for Nvidia's GeForce RTX 4000 series, it was about the Radeon RX 7000 based on the RDNA 3 GPUs Navi 31, 32 and 33 recently rather quiet. Angstronomics has ended this calm without causing any unrest.

GPU key data is condensing

Because if the published information is correct, Angstronomics has confirmed the most recently traded key data and thus the “reduced” execution units of the two large GPUs Navi 31 and Navi 32 compared to older rumors. Angtronomics also reports again that the Navi 31 and Navi 32 appear in chiplet design, while the Navi 33 appears as a “monolithic” one-chip solution and all use GDDR6 on a 384 to 128-bit interface.

(“Plum Bonito”) gfx1101

(“Wheat Nas”) gfx1102

(“Hotpink Bonefish”) Design Chiplet

1 × GDC + 6 × MCD

(~308 mm², ~37.5 mm²) Chiplet

1 × GDC + 4 × MCD

(~200 mm², ~37.5 mm²) Monolithic

One chip (~203 mm²) Manufacturing TSMC N5 (GCD), TSMC N6 (MCD) TSMC N6 GDC configuration 48 WGPs with 12,288 ALUs 30 WGPs with 30 7,680 ALUs 16 WGP with 4,096 ALUs Infinity Cache 96 MB or 192 MB

(6 × 16 or 6 × 32 MB) 64 MB

(4 × 16 MB) 32 MB memory interface 384-bit GDDR6 256-bit GDDR6 128-bit GDDR6 GDC = Graphics Compute Die (processing unit)

MCD = Memory Control Die ( Memory chip incl. Infinity Cache)

WG

With a view to leakers, who recently spoke of AMD having adjusted the GPUs at short notice, the website cannot help but point out that, according to its own information, the key data now presented were finally determined by AMD in 2020.

< h2 class="text-width text-h2" id="section_surprisingly_little_infinity_cache">Surprisingly little infinity cache

The fact that AMD is likely to come onto the market again without a faster, but also thirsty GDDR6X is again due to the fast Infinity Cache cache, which, according to Angstronomics, could be smaller than previously assumed and therefore also smaller than in the last generation. Because while the Navi 21 128 and Navi 22 still offered 96 MB, the Navi 31 and Navi 32 should only have 96 and 64 MB respectively. Only Navi 33 would draw level with its predecessor with 32.

In the case of Navi 31, a variant with a 192 MB infinity cache is also not yet off the table, which would stack two 16 MB chips in each of the six MCDs. That would be more expensive and hardly provide any more performance, according to Angstronomics, but could be a unique selling point for a top model like a Radeon RX 7900 XT. According to the current status, however, this step is not planned for Navi 32.

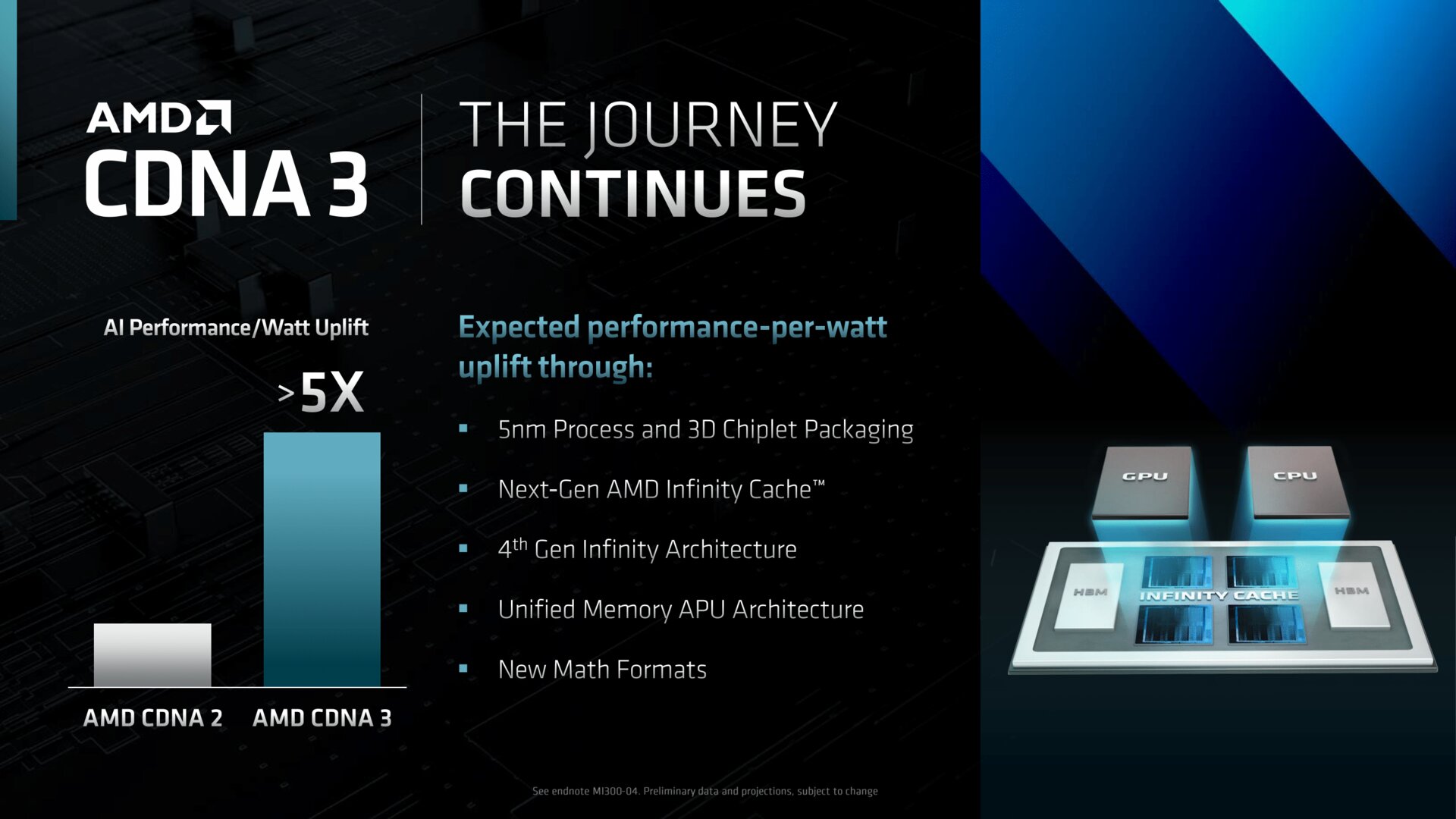

AMD had only discussed “3D Chiplet Packaging” for CDNA 3 when announcing RDNA 3 and CDNA 3 , with RDNA 3 again only from “Advanced Chiplet Packaging”, but rumors that in the end chiplets will also be stacked with RDNA 3 persist.

Without making any adjustments to the cache itself, 96, 64 and 32 MB undoubtedly don't seem like much at first, because the new GPUs will offer more performance than their predecessors, qualify for higher resolutions and therefore be able to store less data required for calculation in the (smaller) cache – even with Navi 24, 32 MB was too tight for everything above Full HD.

It remains to be seen whether these capacities will come true, or what else AMD has changed to counteract this bottleneck.

CDNA 3 with 3D chiplet packaging (image: AMD)

CDNA 3 with 3D chiplet packaging (image: AMD)Chip size information

An interesting piece of new information is the chip sizes published by Angstronomics which, if true, will show how many more execution units AMD will get by switching from TSMC N7 to N5 (GDC Navi 31 and 32) or N6 (Navi 33) on the same area. Navi 24 as a tiny N6 premiere had already indicated that.

(308 mm² + 6 × 37.5 mm²) 519 mm² 425 mm²

(200 mm² + 6 × 37.5 mm²) 336 mm² 203 mm² 237 mm²

Not only the process, but also adjustments to the architecture from RDNA 2 to RDNA 3 have an impact on the further sharp increase in area efficiency. According to Angstronomics, in addition to increasing the performance per watt (officially > 50 percent), AMD also put the performance per area at the top of the specifications. The smaller the chip, the more chips fit on a wafer – and payment is made in exposed wafers, which lowers the cost per chip as the number of chips on the wafer increases. In addition, a wafer yields more chips for more graphics cards to be sold.

Navi-31 reference with two 8-pin connectors

Speaking of graphics cards: Angstronomics also assumes that only Navi 31 will appear on desktop graphics cards this year, their reference designs with a revised 3-fan design, but “only” with two 8-pin PCI connectors should appear, which officially allows a maximum of 375 watts TDP. Navi 32 will not follow until next year. In all probability, this also applies to Navi 33, where the focus is on notebooks. For this reason, the GPU is also pin-compatible with Navi 23.

Is AMD considering dual Navi-32?

< p class="p text-width">3DCenter wrote down an interesting thought about the latest rumours: The fact that two Navi 32, each with 7,680 ALUs, result in a total of 15,360 ALUs, which for a long time corresponded to the status of the Navi 31 rumor mill mean that AMD has internally considered such a variant. Since such a variant no longer appeared in the more credible rumors about Navi 3x, AMD may have given up on this goal in the meantime, or never pursued it.