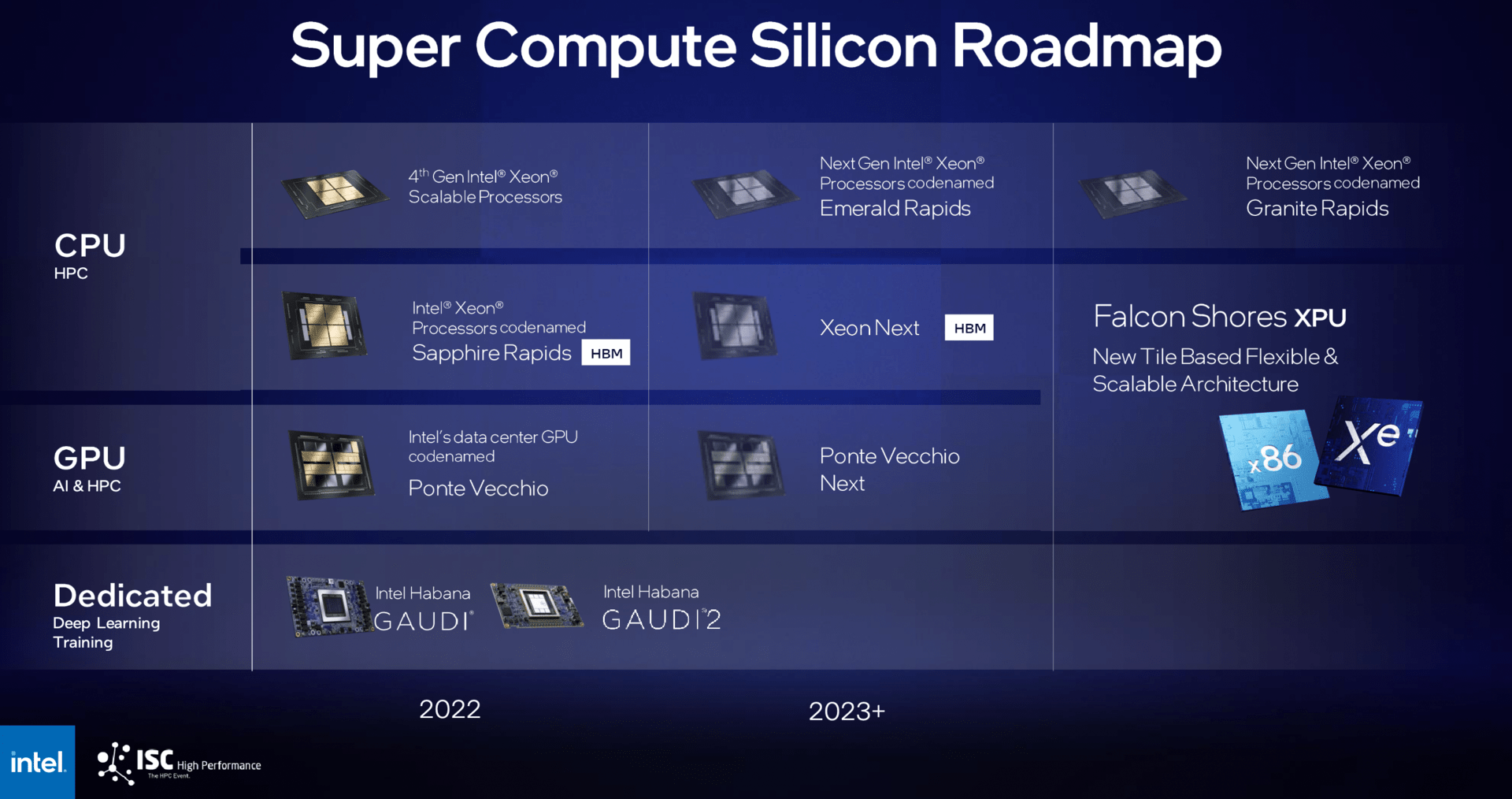

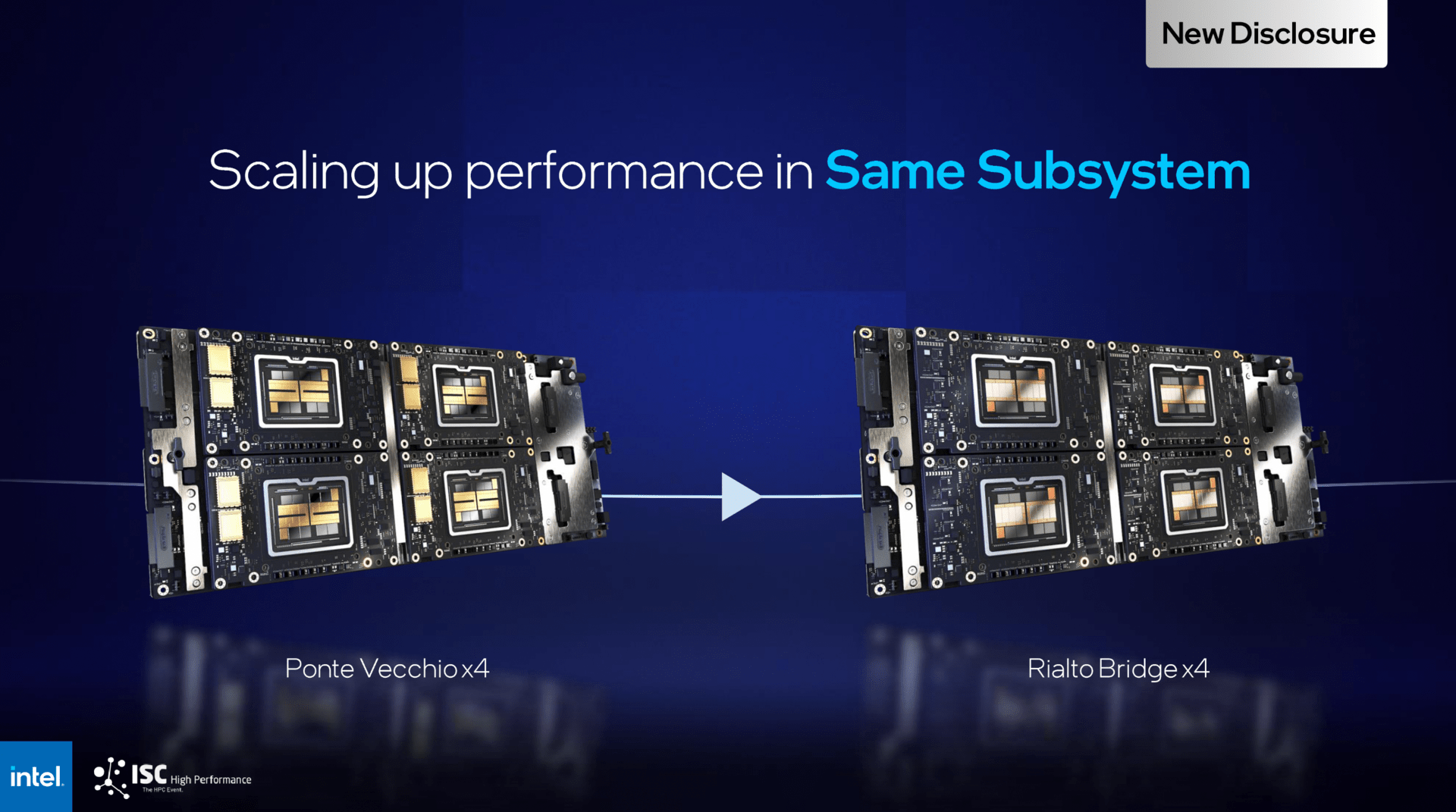

At the ISC 2022 in Hamburg, Intel revealed the first details about the next-gen HPC GPUs Rialto Bridge as the direct successor to Ponte Vecchio and Falcon Shores. Rialto Bridge increases the number of Xe cores by 25 percent as a “tick” with new process technologies, Falcon Shores is supposed to do everything differently from 2024.

Benchmarks for Sapphire Rapids with HBM

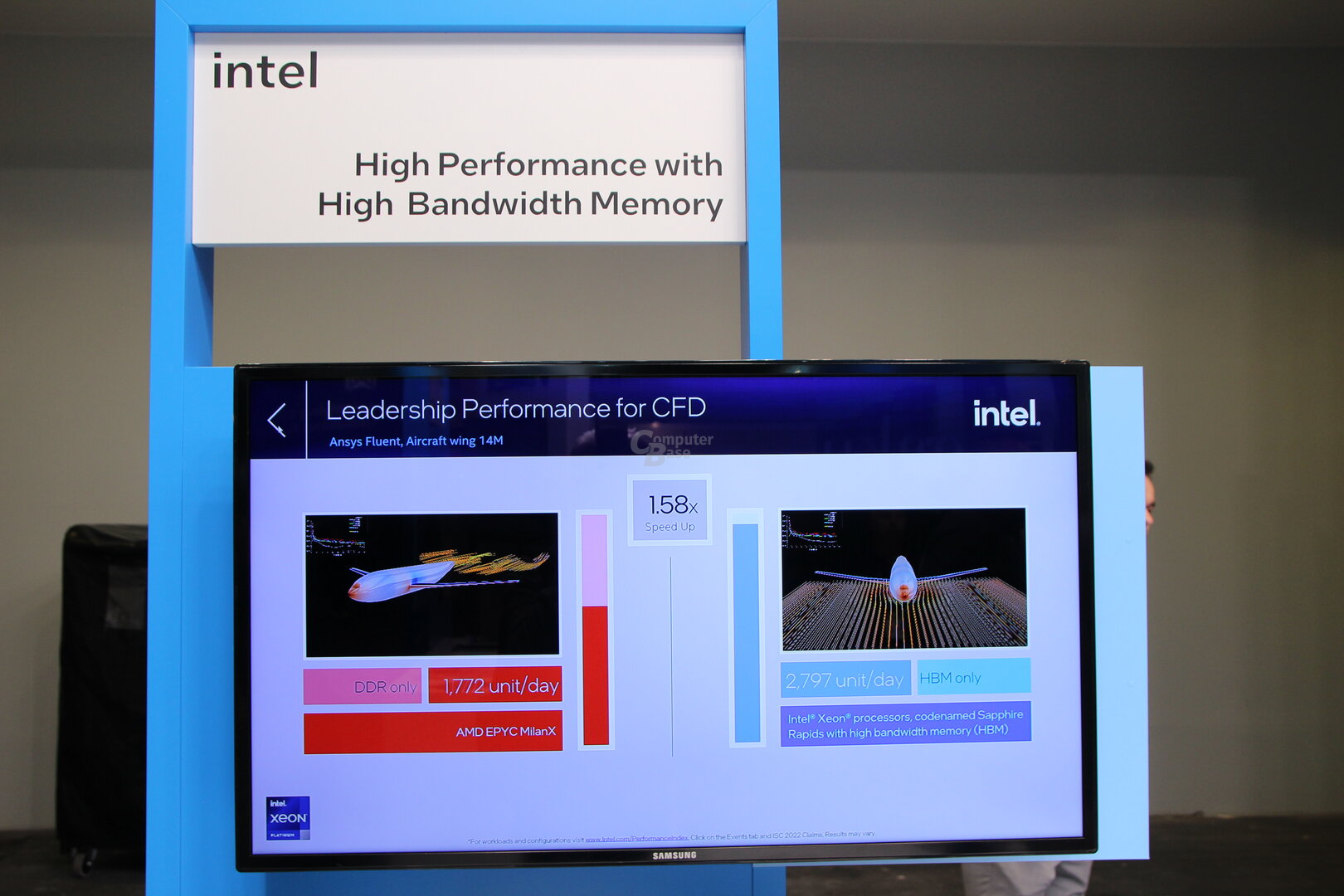

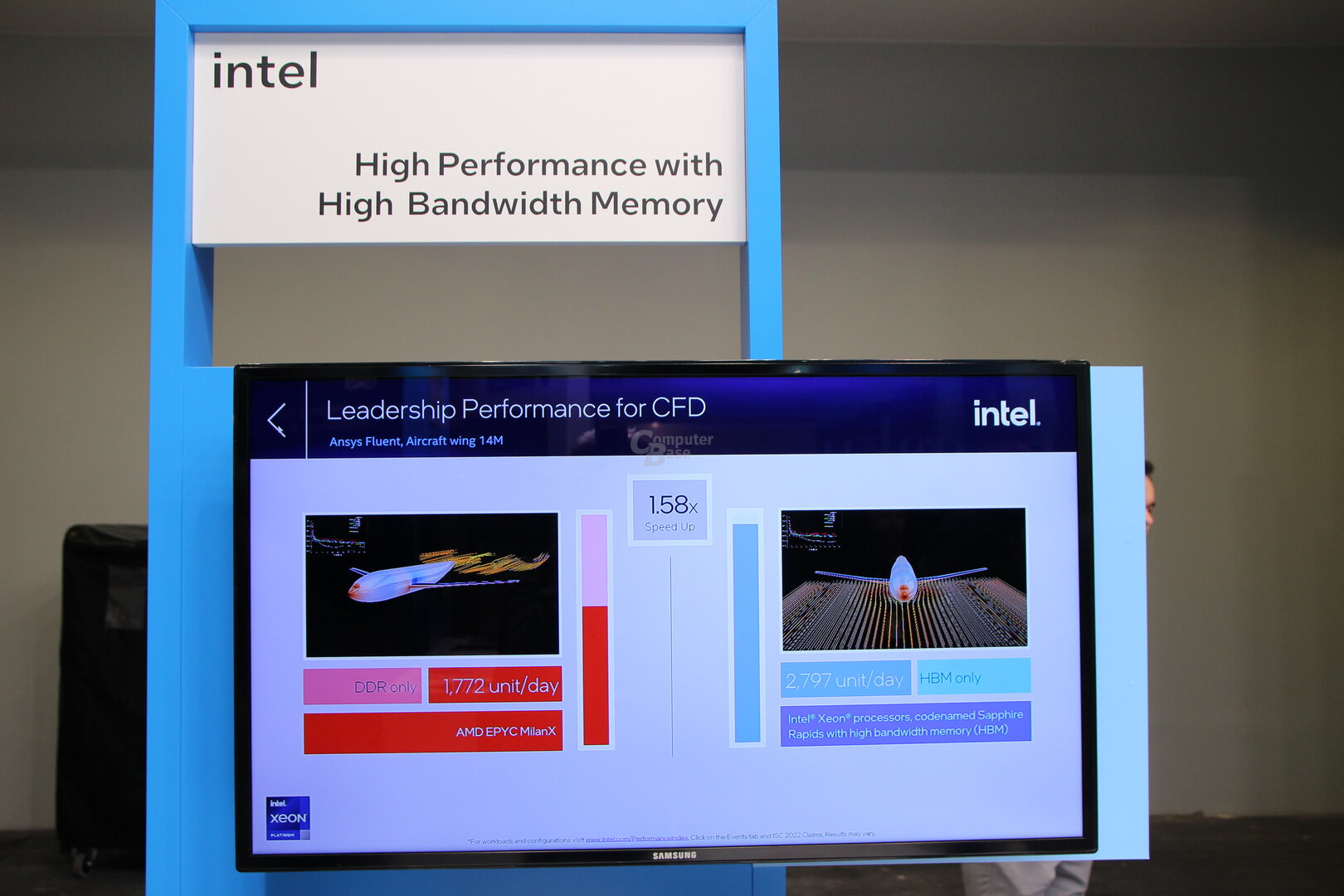

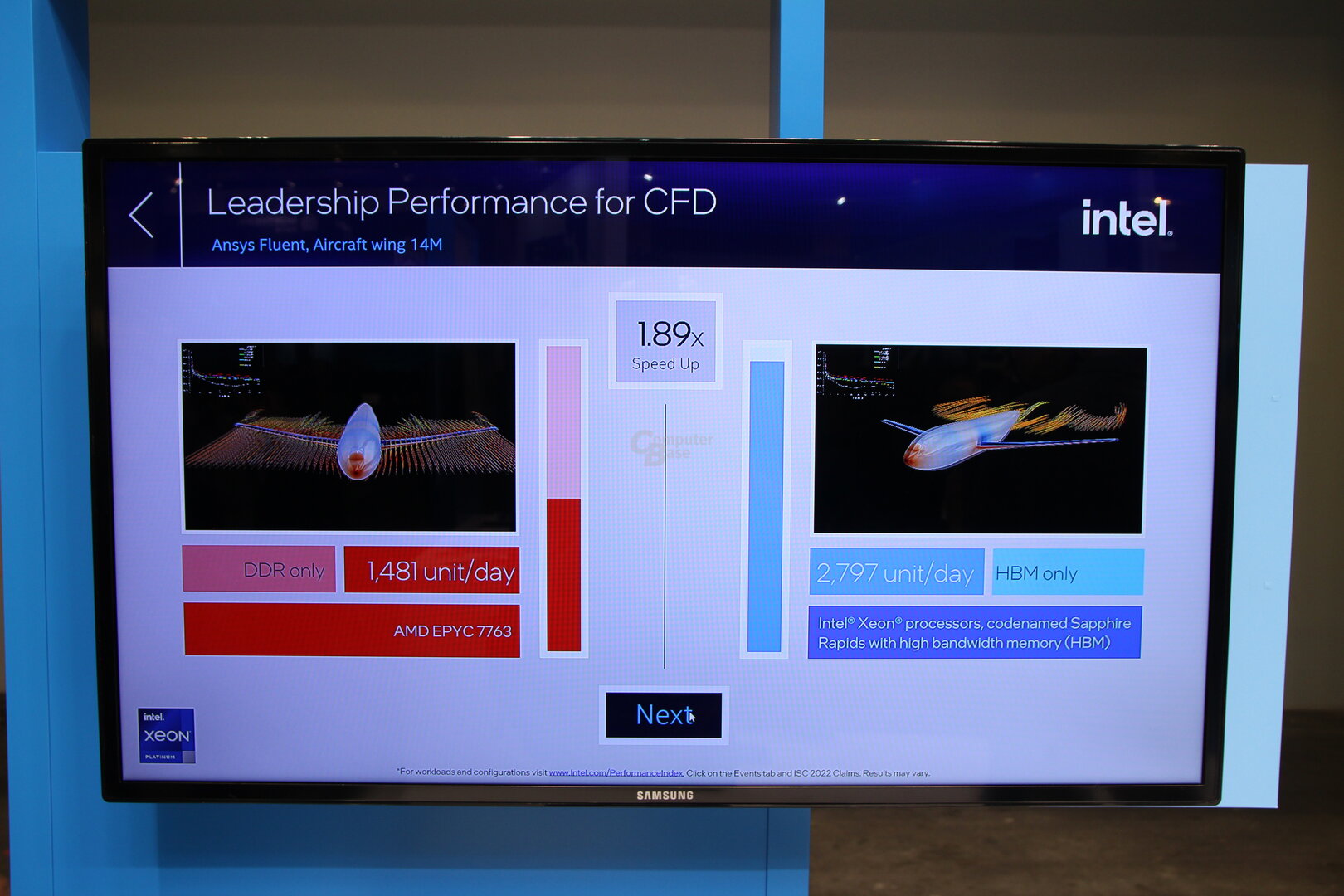

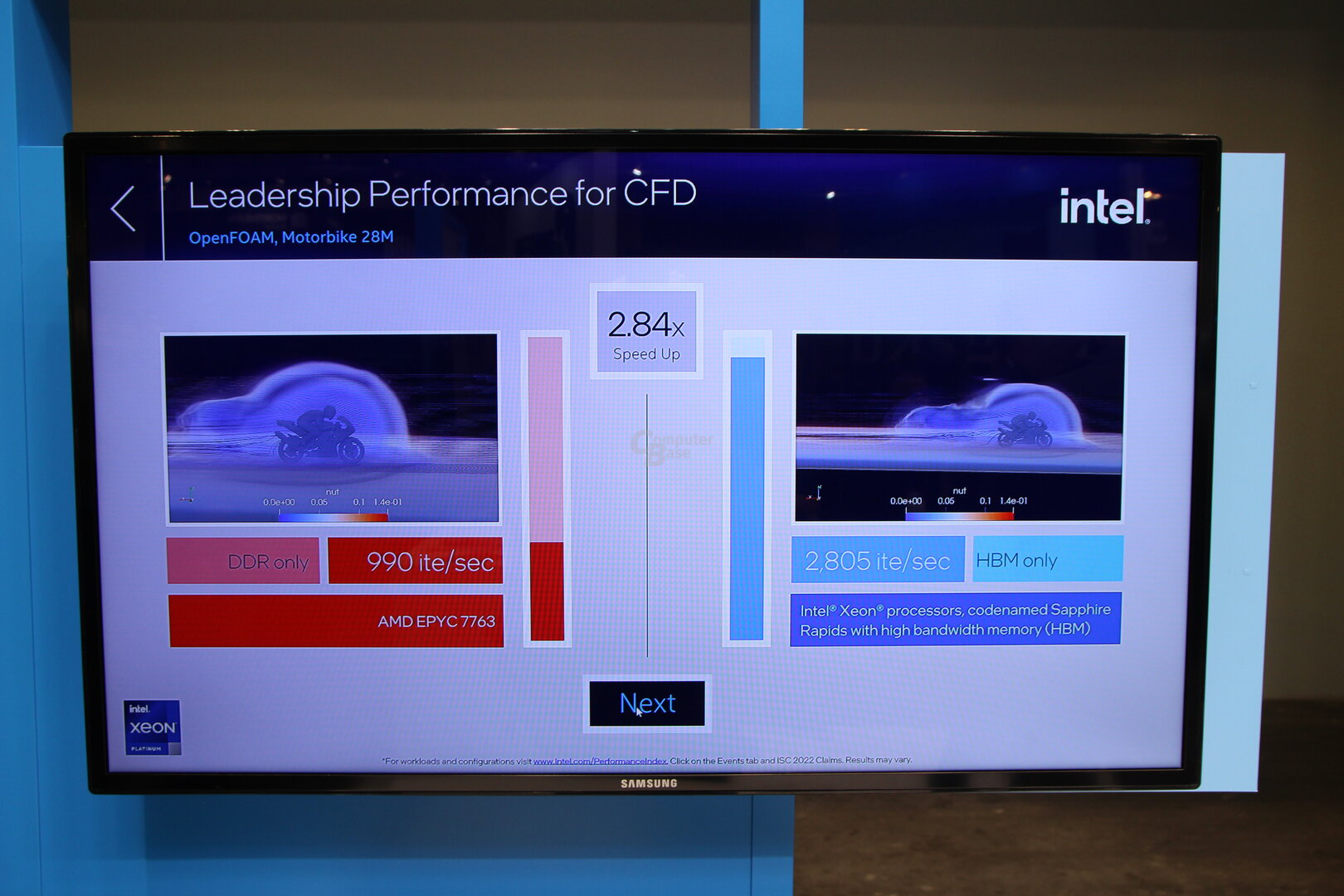

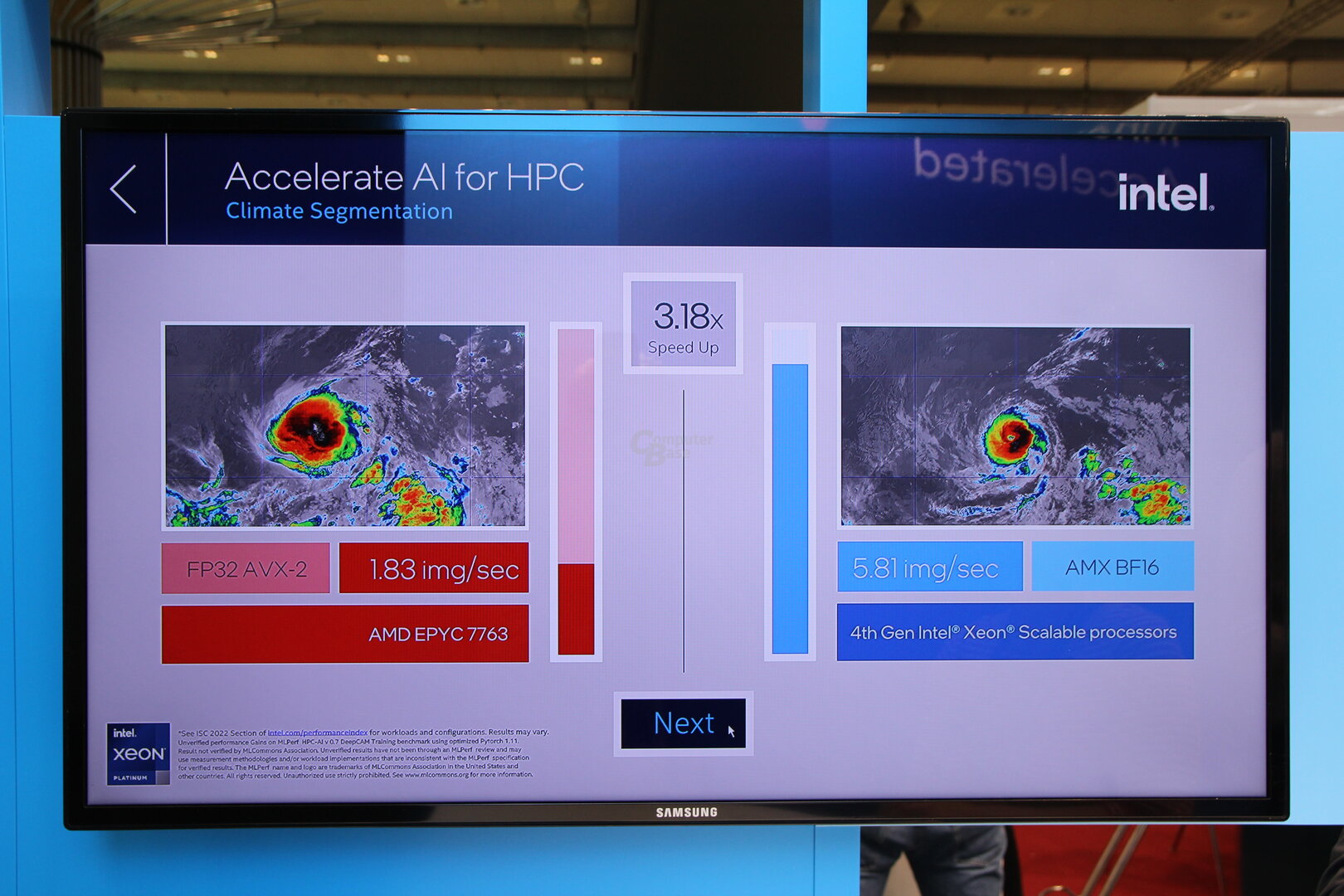

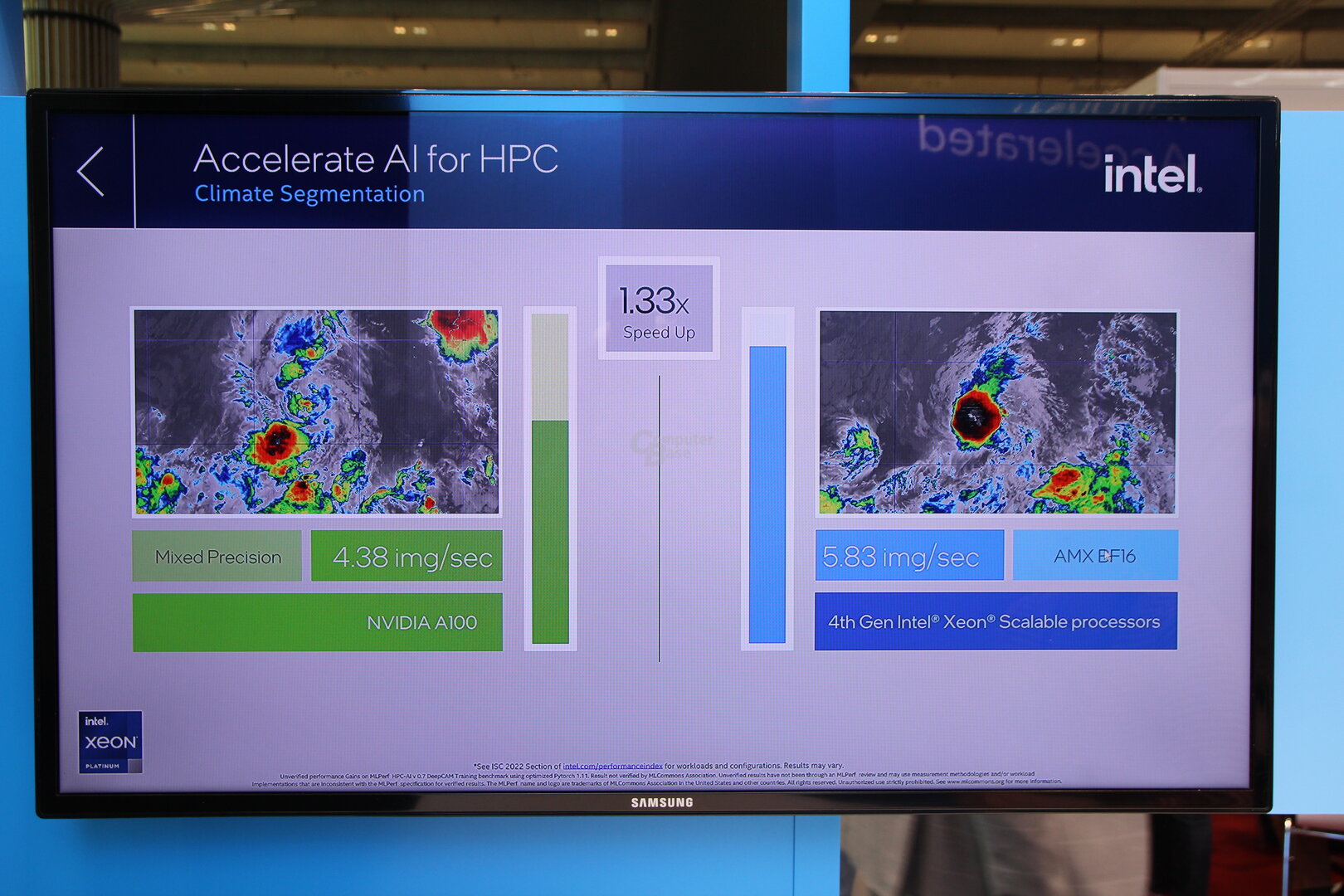

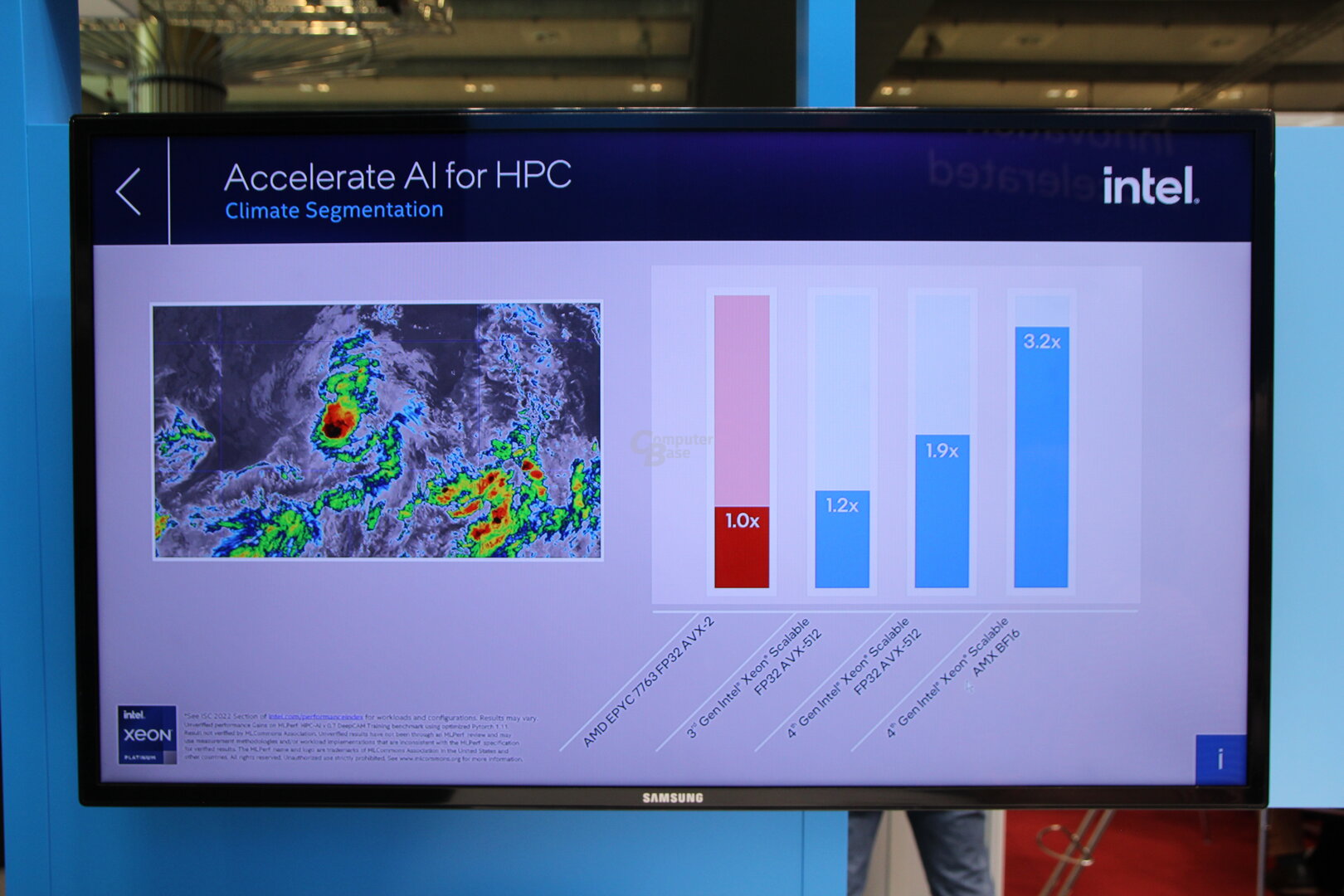

But first, the topic was Sapphire Rapids, the server variant of the Alder Lake architecture. At the fair, Intel showed these chips in selected benchmarks without, but above all with HBM. This unique selling point has also been in the works since 2018, the manufacturer explained in an interview with ComputerBase. At its own stand, Intel proudly showed applications in which the competition naturally does not fare well. The new processor was only operated with HBM, DDR5 was completely dispensed with as an addition to the system.

-

Intel demos from SPR with HBM

Intel demos from SPR with HBM

Image 1 of 6

Intel demos from SPR with HBM

Intel demos from SPR with HBM  Intel demos from SPR with HBM

Intel demos from SPR with HBM  Intel demos from SPR with HBM

Intel demos from SPR with HBM  Intel demos by SPR

Intel demos by SPR  SPR Intel Demos

SPR Intel Demos  SPR Intel Demos

SPR Intel Demos Of course, this is a special case, because the size is one of the limitations here: There is no more than 64 GB HBM per CPU. Two CPUs can then share the 128 GB, but with a corresponding latency penalty for communication with each other.

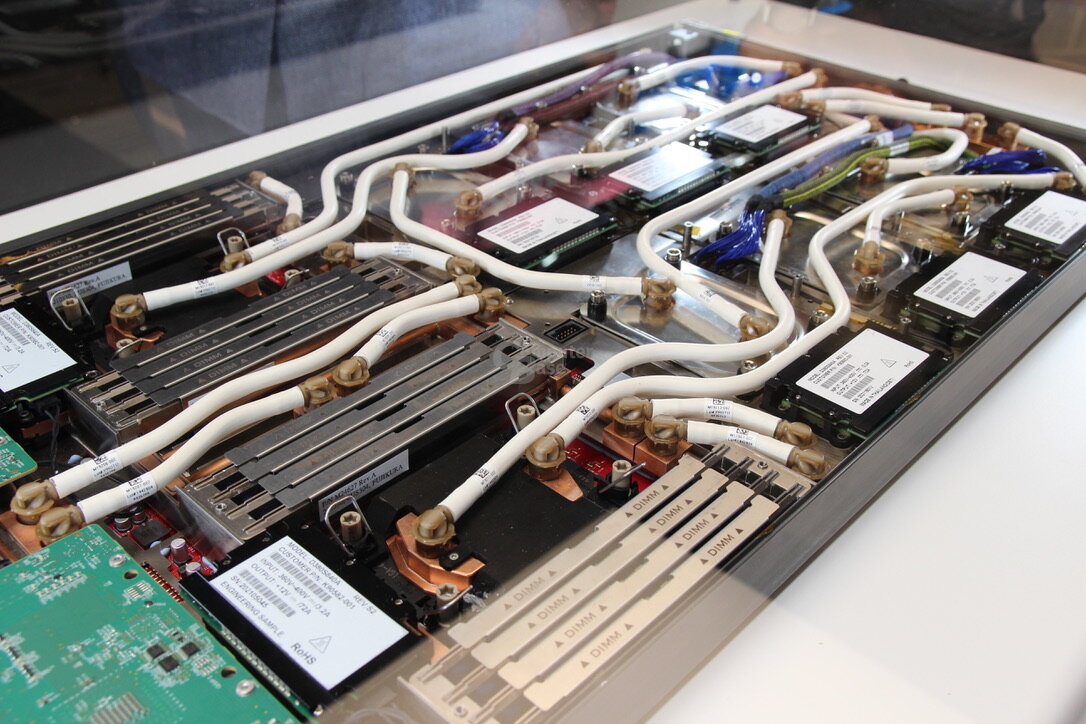

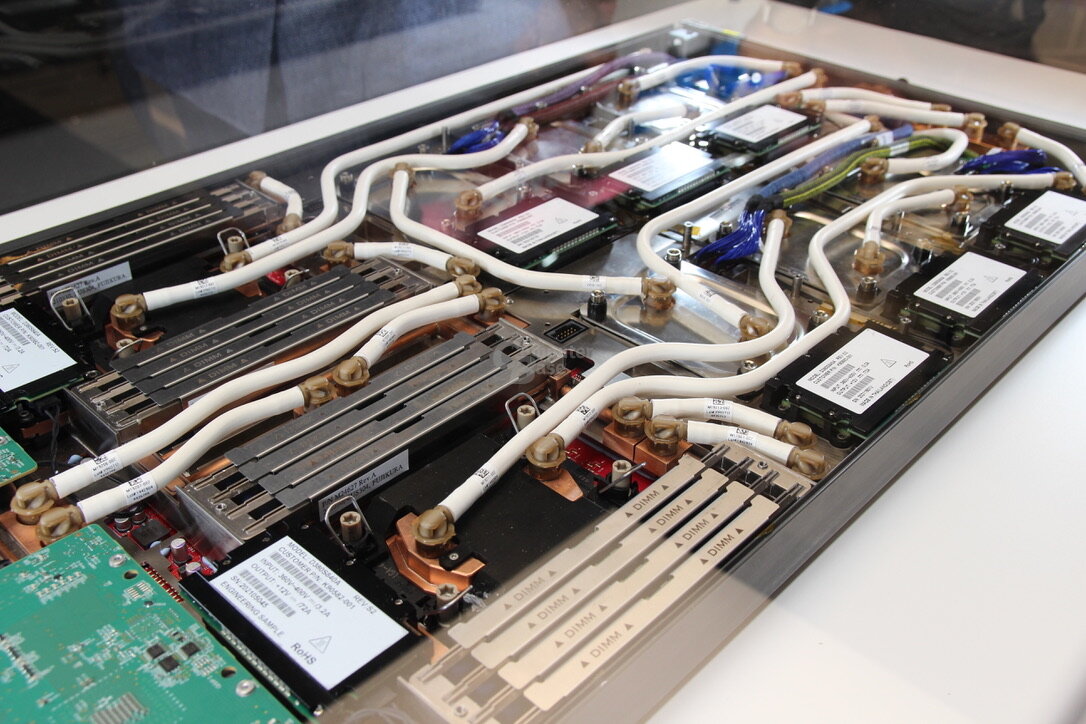

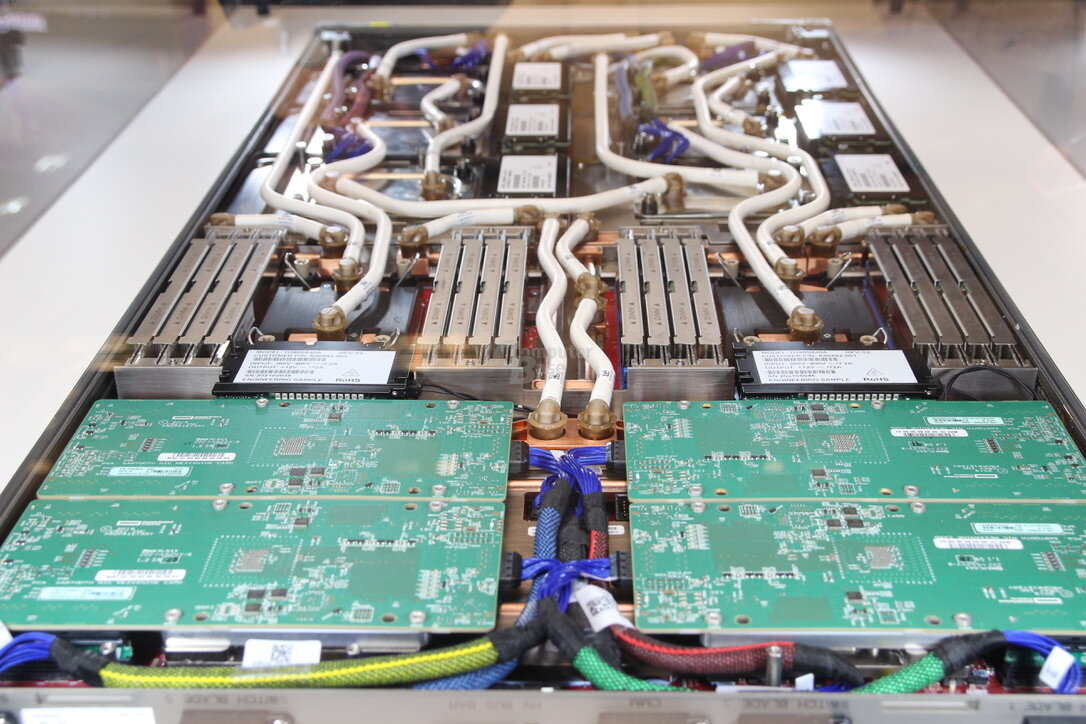

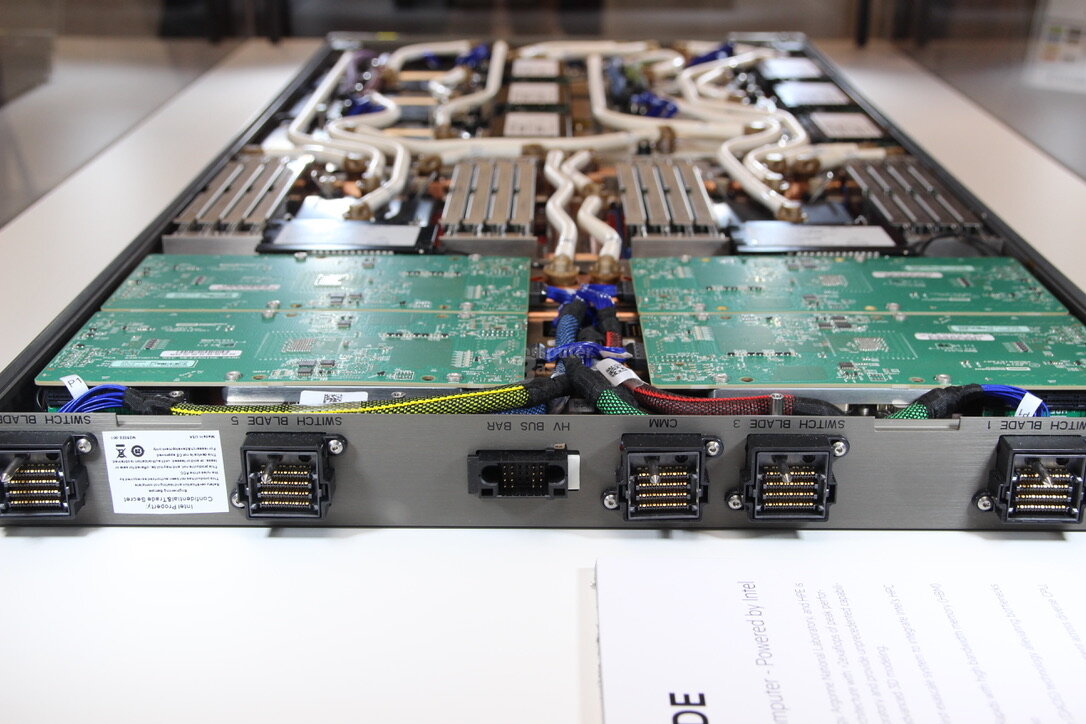

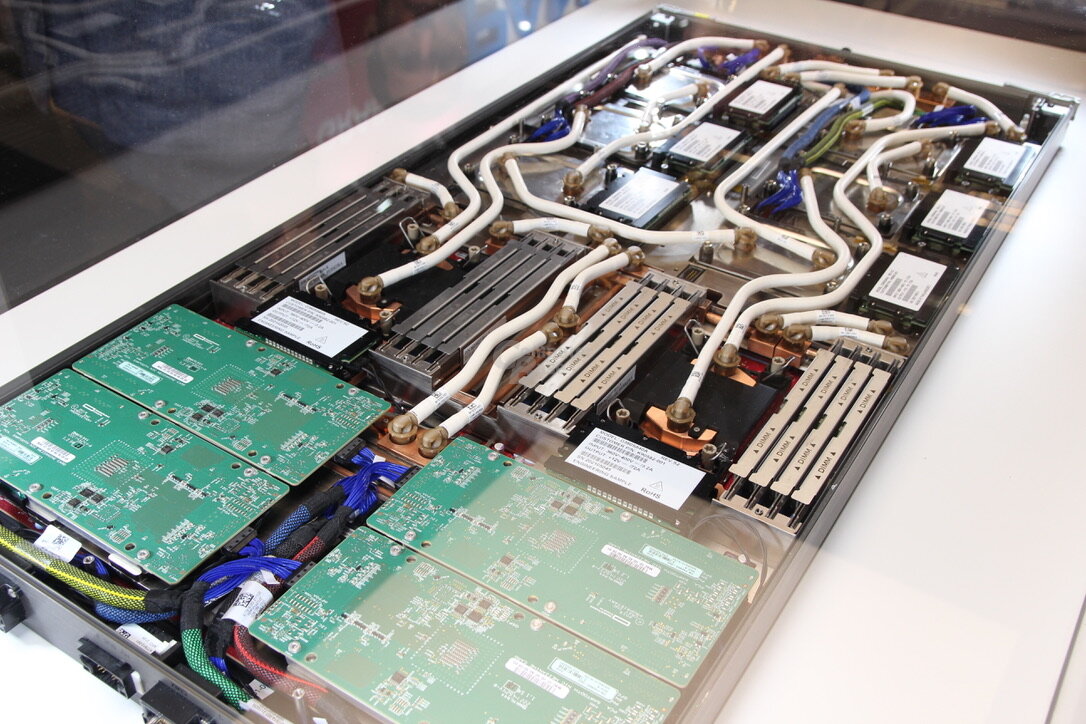

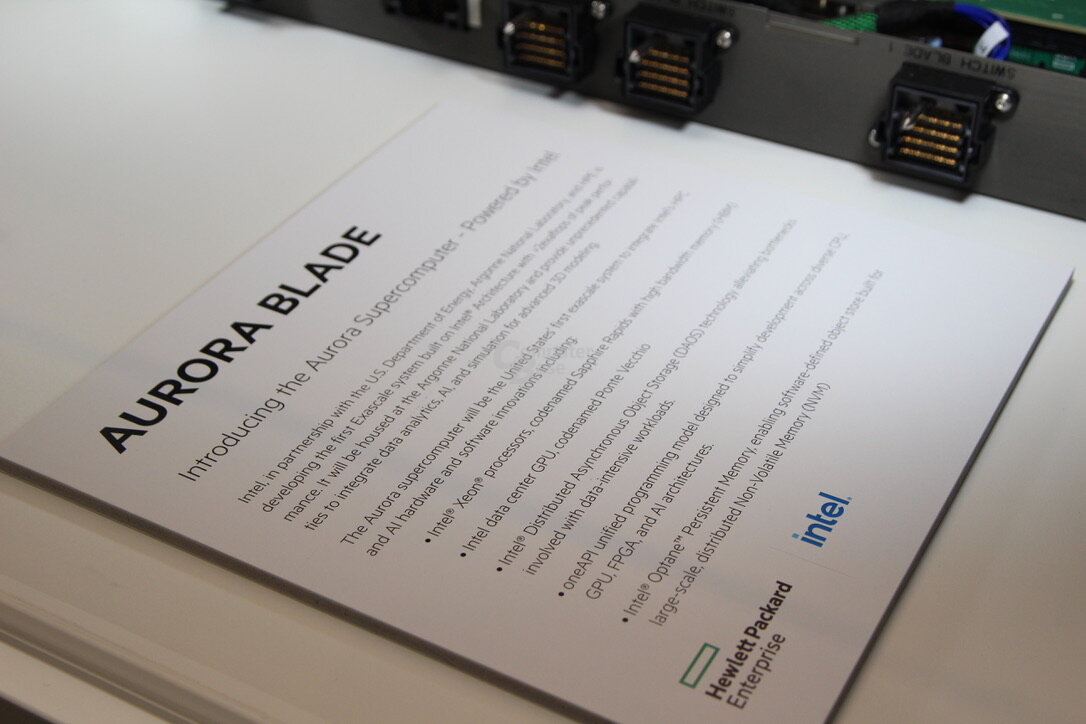

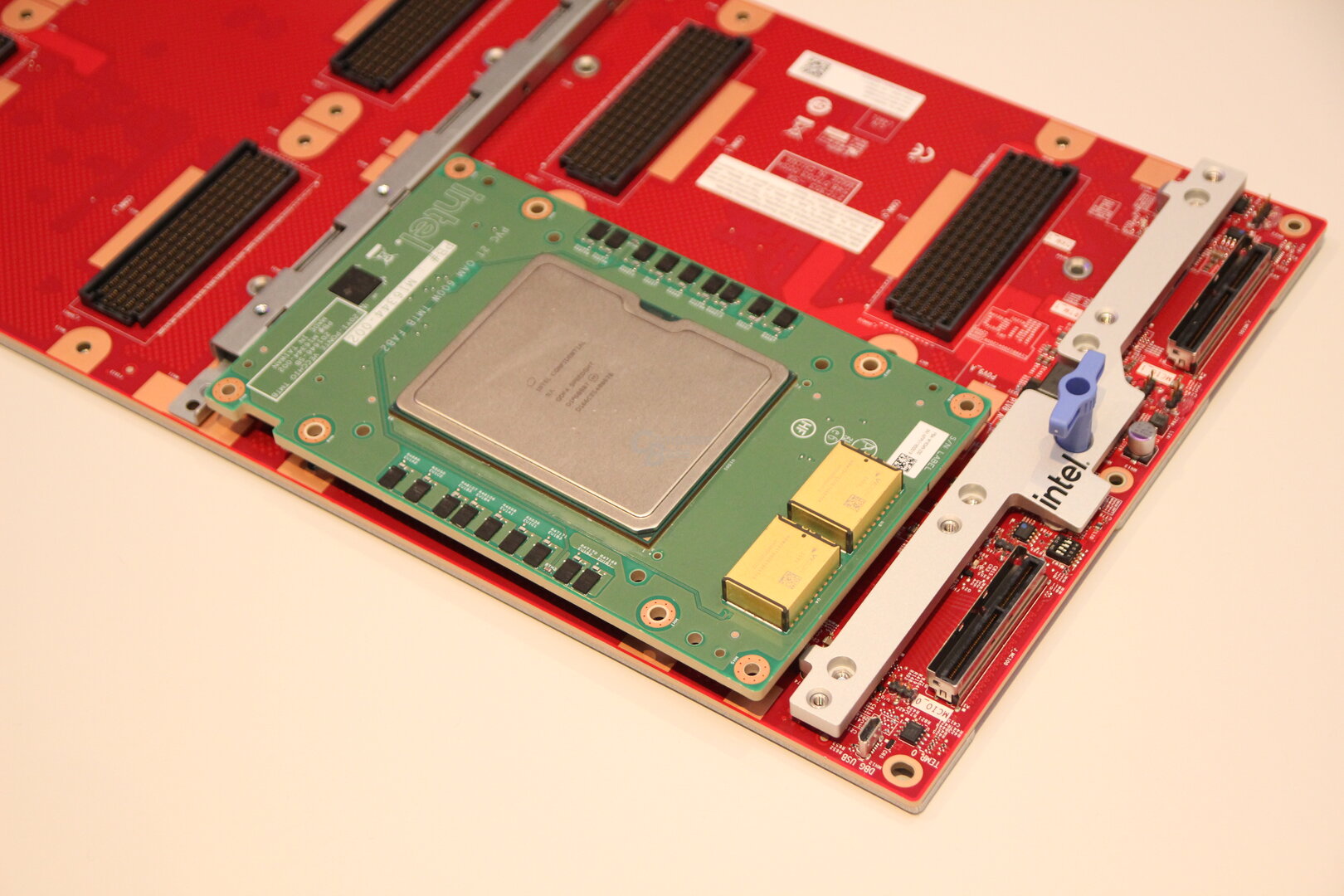

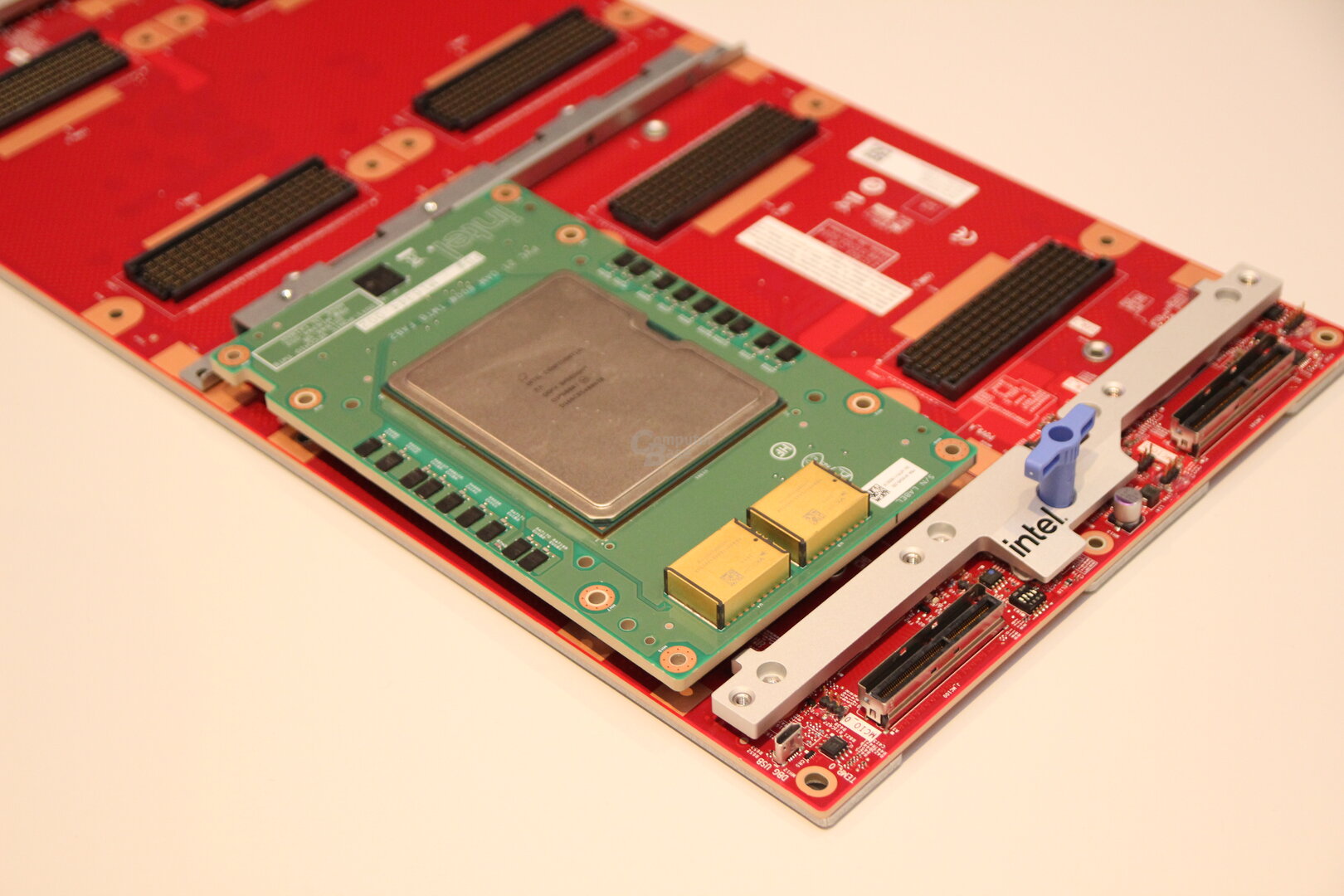

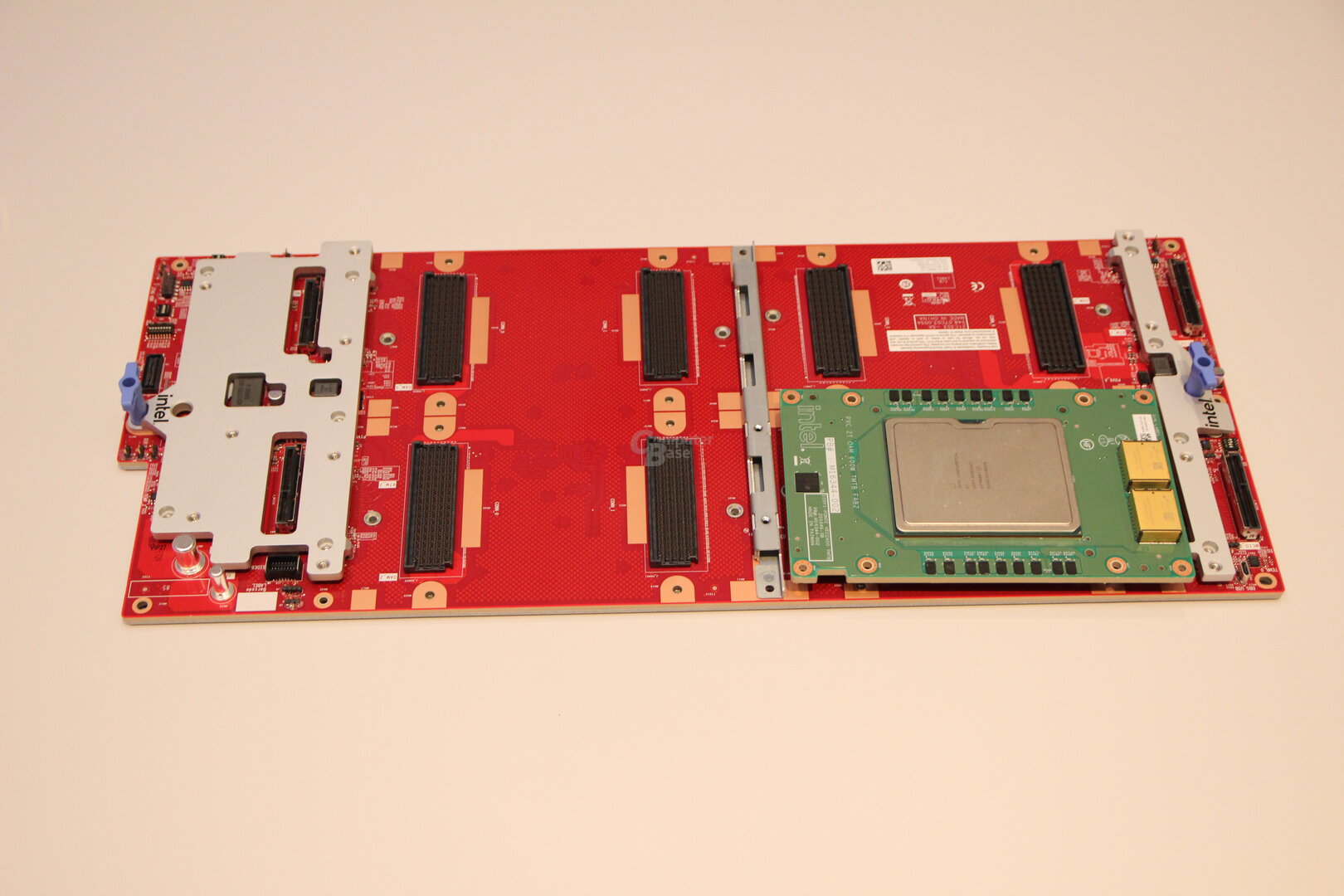

Sapphire Rapids with HBM is a flagship for the supercomputer Aurora. The 2 ExaFLOPS supercomputer is said to be equipped with exactly these solutions and three times the amount of Ponte Vecchio GPUs later in the year. Intel is showing a suitable blade together with HPE at the trade fair. HPE is also exhibiting a blade of the first ExaFLOPS supercomputer Frontier with CPUs and GPUs from AMD.

Aurora Blade with two Sapphire Rapids and six Ponte Vecchio

Aurora Blade with two Sapphire Rapids and six Ponte Vecchio image 1 of 7

Aurora Blade with two Sapphire Rapids and six Ponte Vecchio

Aurora Blade with two Sapphire Rapids and six Ponte Vecchio  Aurora Blade with two Sapphire Rapids and six Ponte Vecchio

Aurora Blade with two Sapphire Rapids and six Ponte Vecchio  Aurora Blade with two Sapphire Rapids and six Ponte Vecchio

Aurora Blade with two Sapphire Rapids and six Ponte Vecchio  Aurora Blade with two Sapphire Rapids and six Ponte Vecchio

Aurora Blade with two Sapphire Rapids and six Ponte Vecchio  Aurora Blade with two Sapphire Rapids and six Ponte Vecchio

Aurora Blade with two Sapphire Rapids and six Ponte Vecchio  Aurora Blade with two Sapphire Rapids and six Ponte Vecchio

Aurora Blade with two Sapphire Rapids and six Ponte Vecchio  Aurora Blade with two Sapphire Rapids and six Ponte Vecchio

Aurora Blade with two Sapphire Rapids and six Ponte Vecchio The second half of 2022 is still on the books as the release date. The HBM variant was supposed to appear later, but as a result of the delays, the normal Xeon and the HBM variant have moved a little closer together again.

Sapphire Rapids will have a long lifetime ultimately not granted anyway, because within a year already Emerald Rapids and then Granite Rapids should appear. The cadence of four to five quarters for new products should apply in every area, explained Jeff McVeigh as head of the supercomputer division at Intel.

Intel roadmap for supercomputers (Image: Intel)

Intel roadmap for supercomputers (Image: Intel) Rialto Bridge will be the successor to Ponte Vecchio

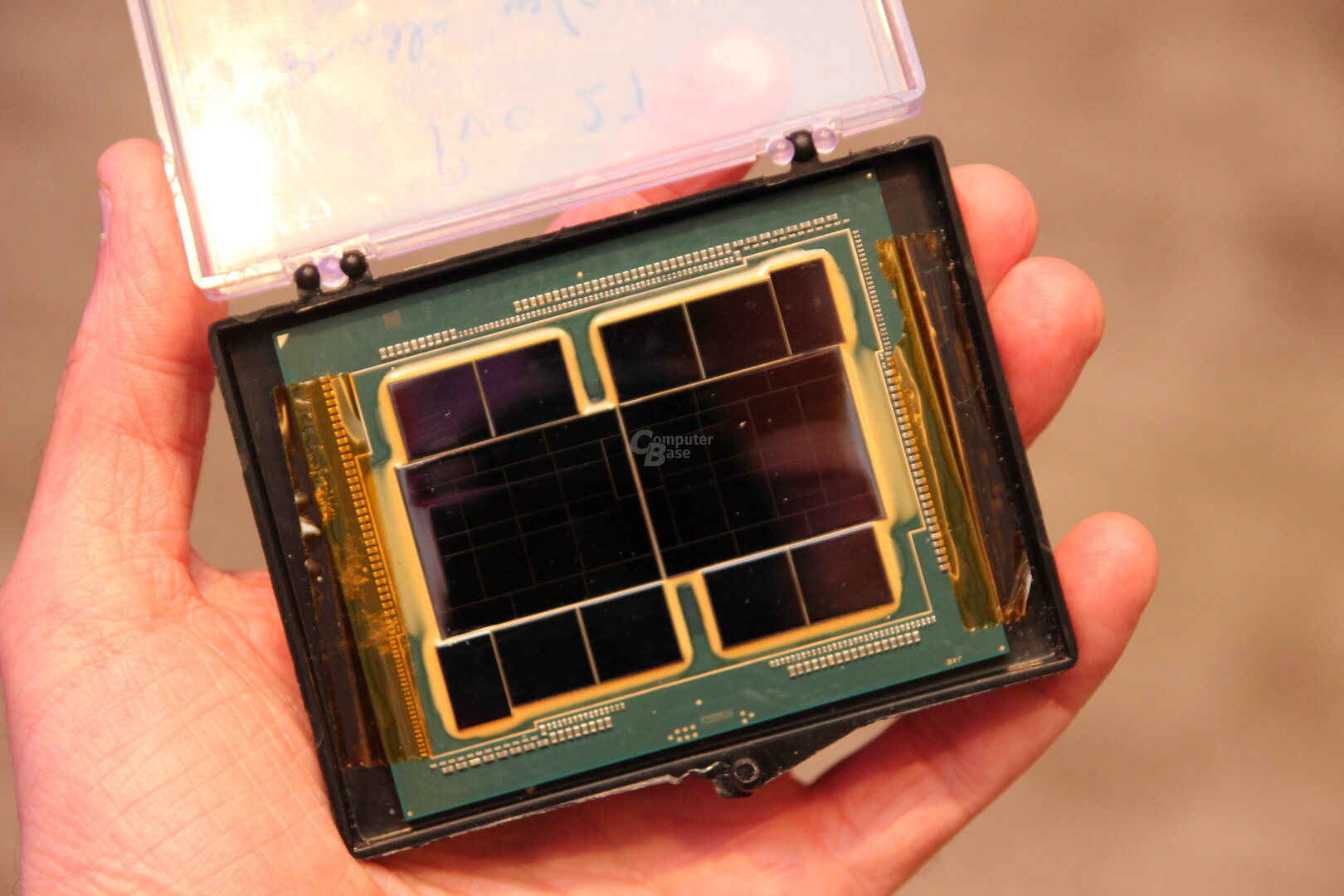

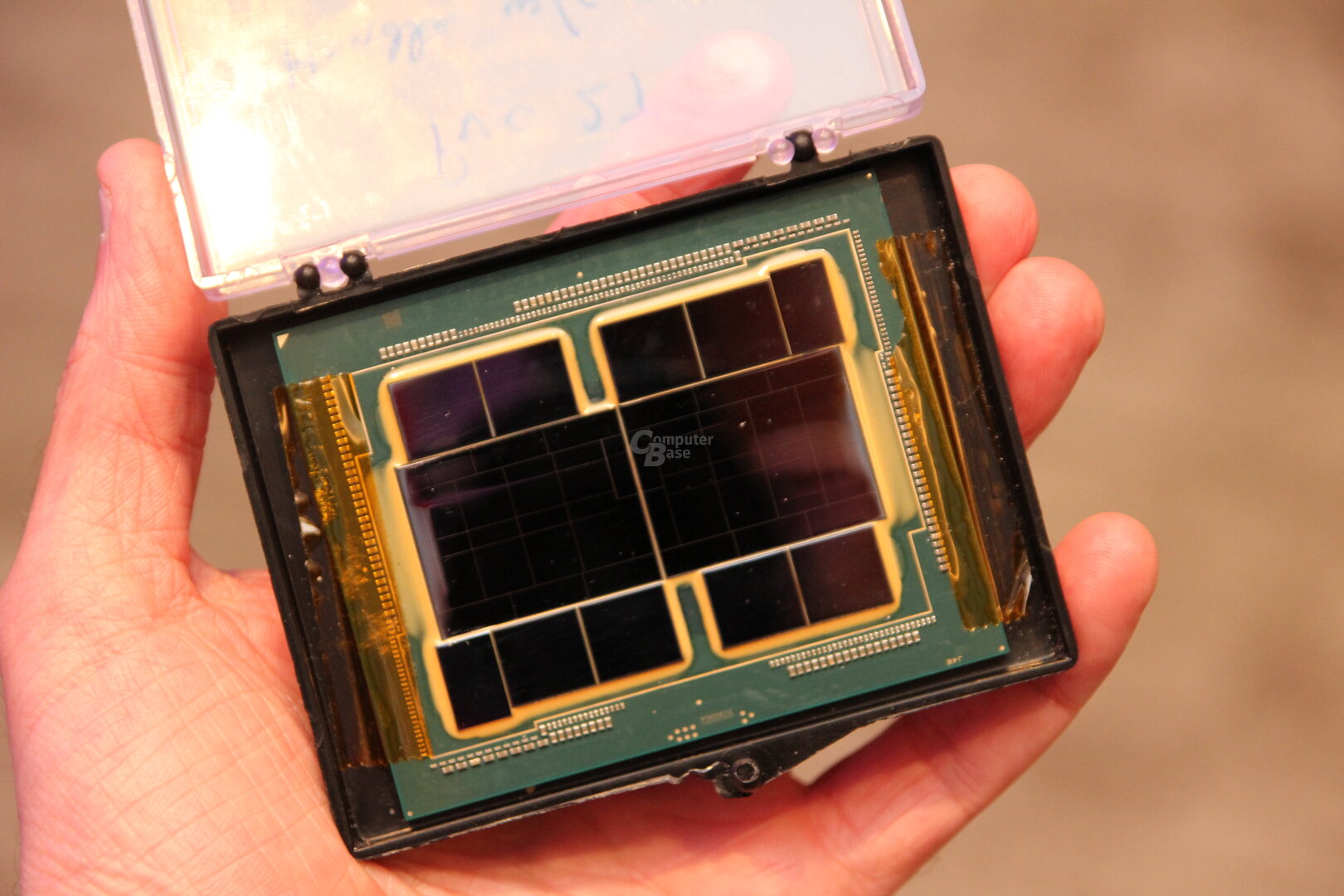

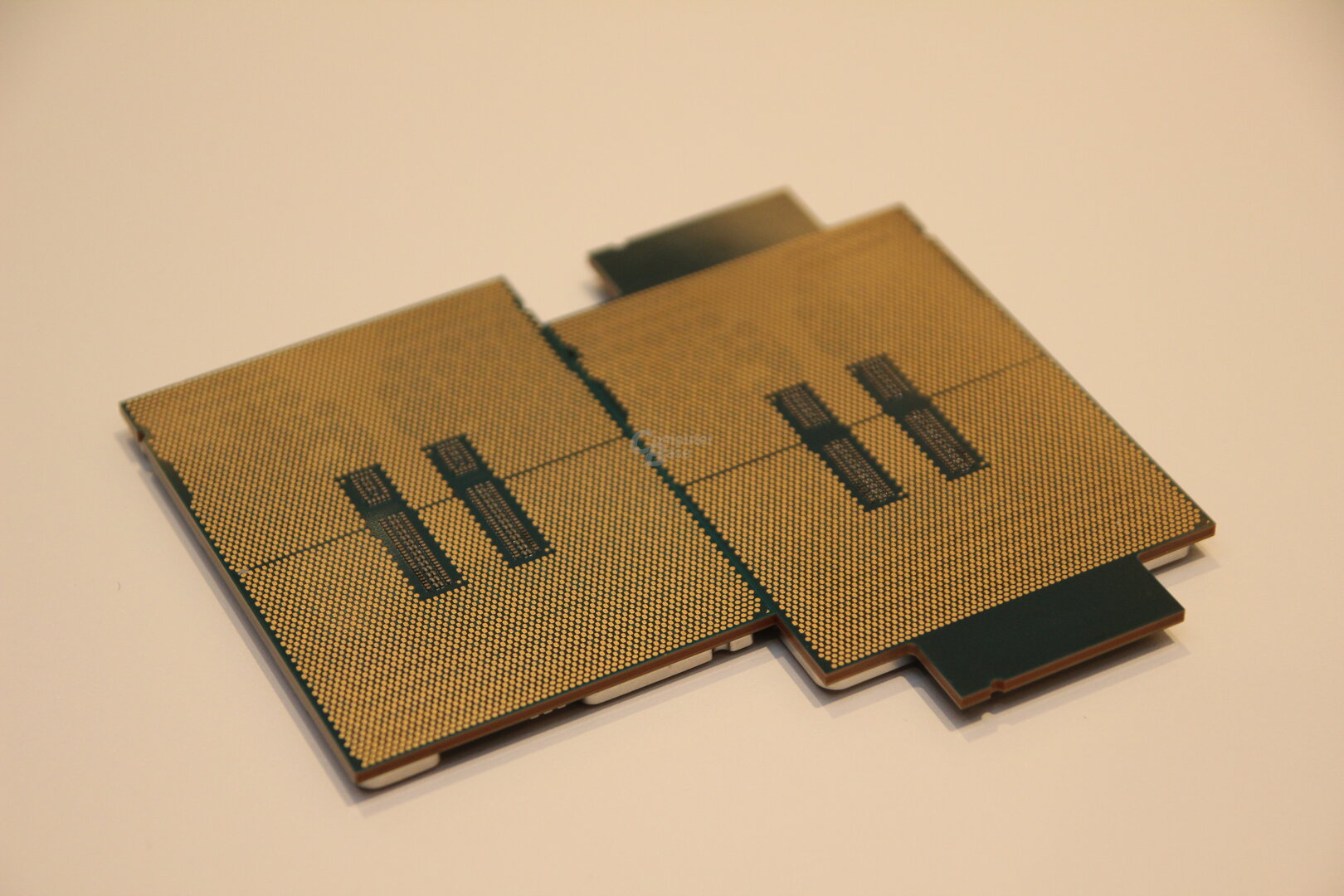

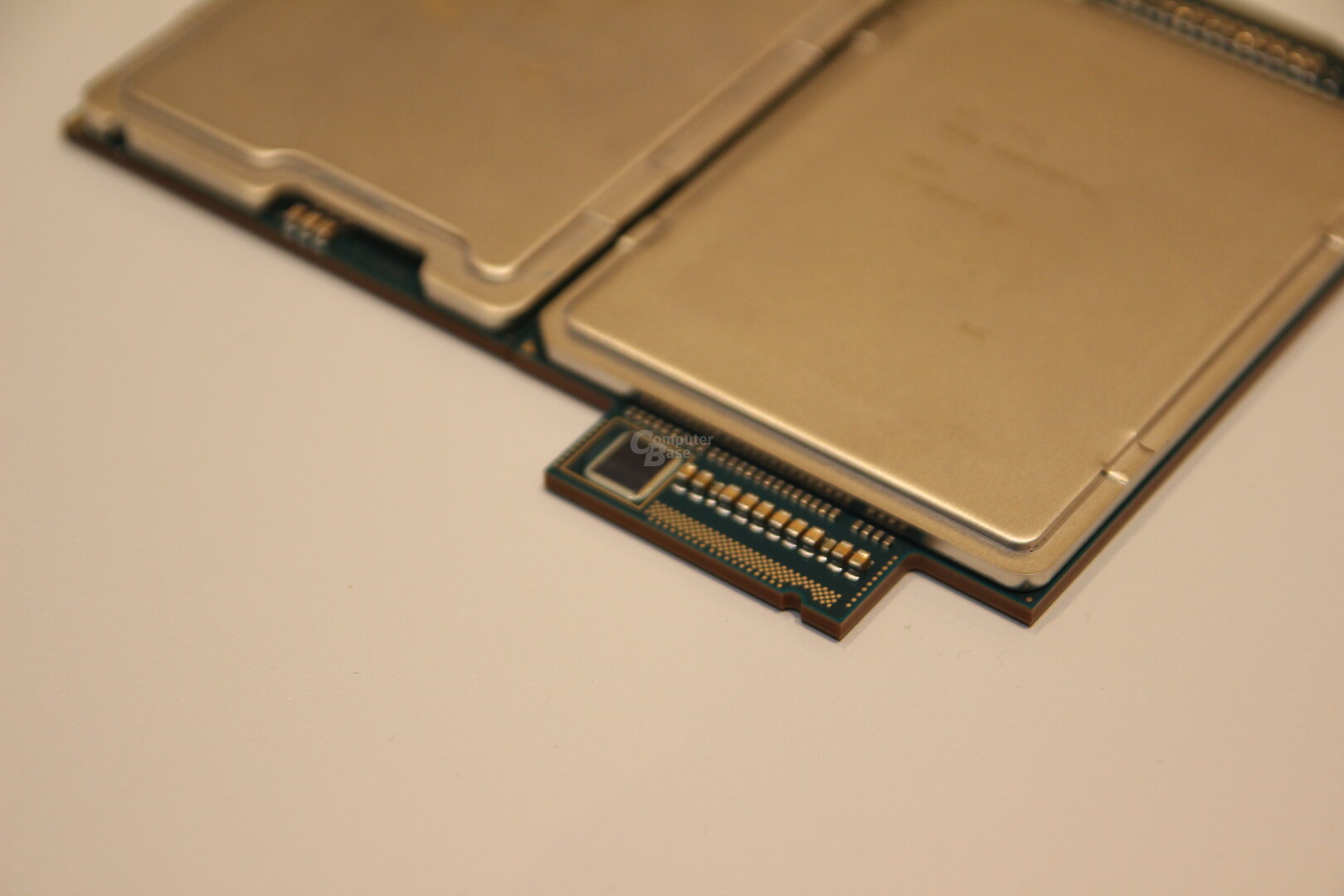

Intel wants to deliver the successor to Ponte Vecchio as early as mid-2023: Rialto Bridge. Ponte Vecchio is the multi-chip approach based HPC GPU based on the Xe architecture.

-

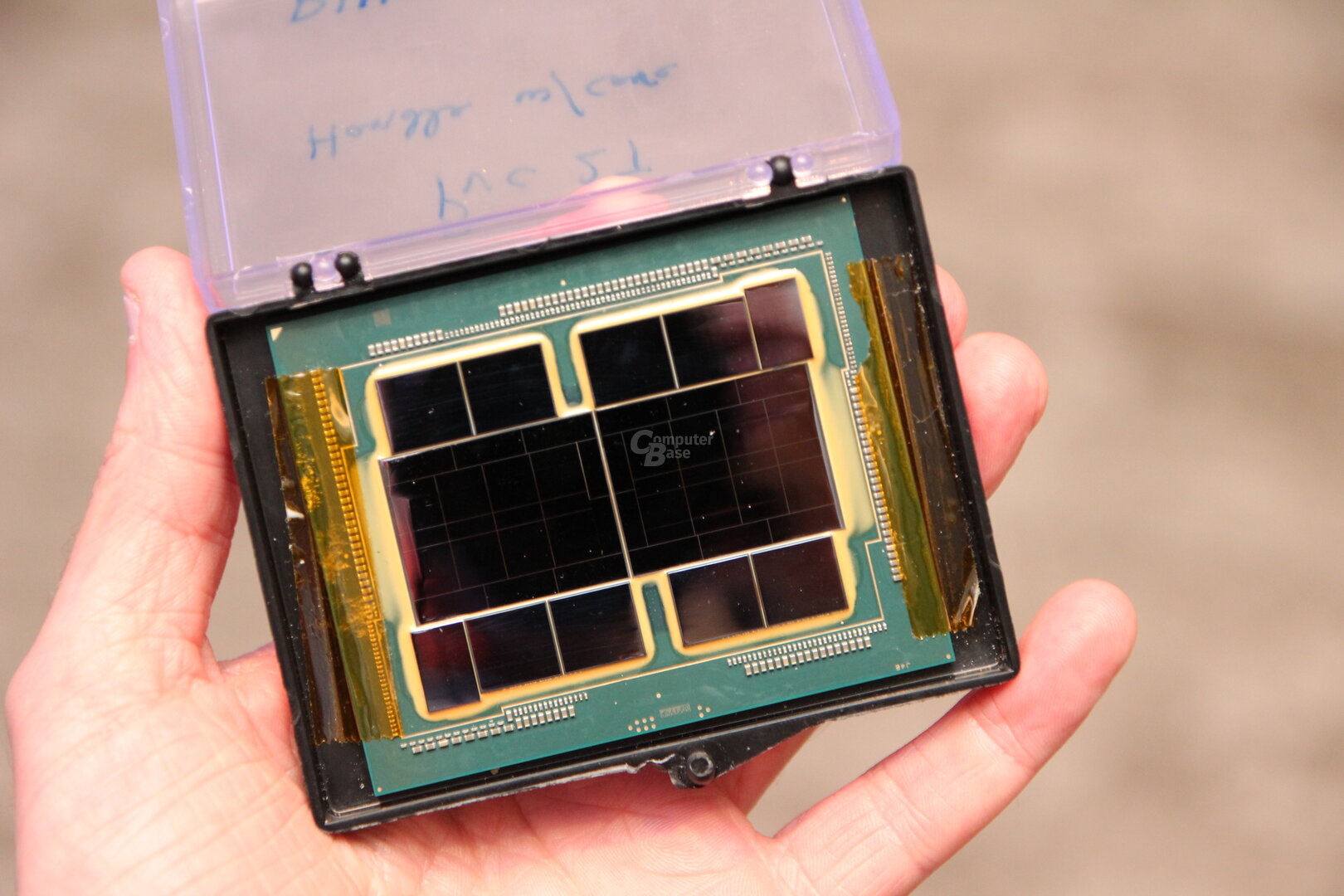

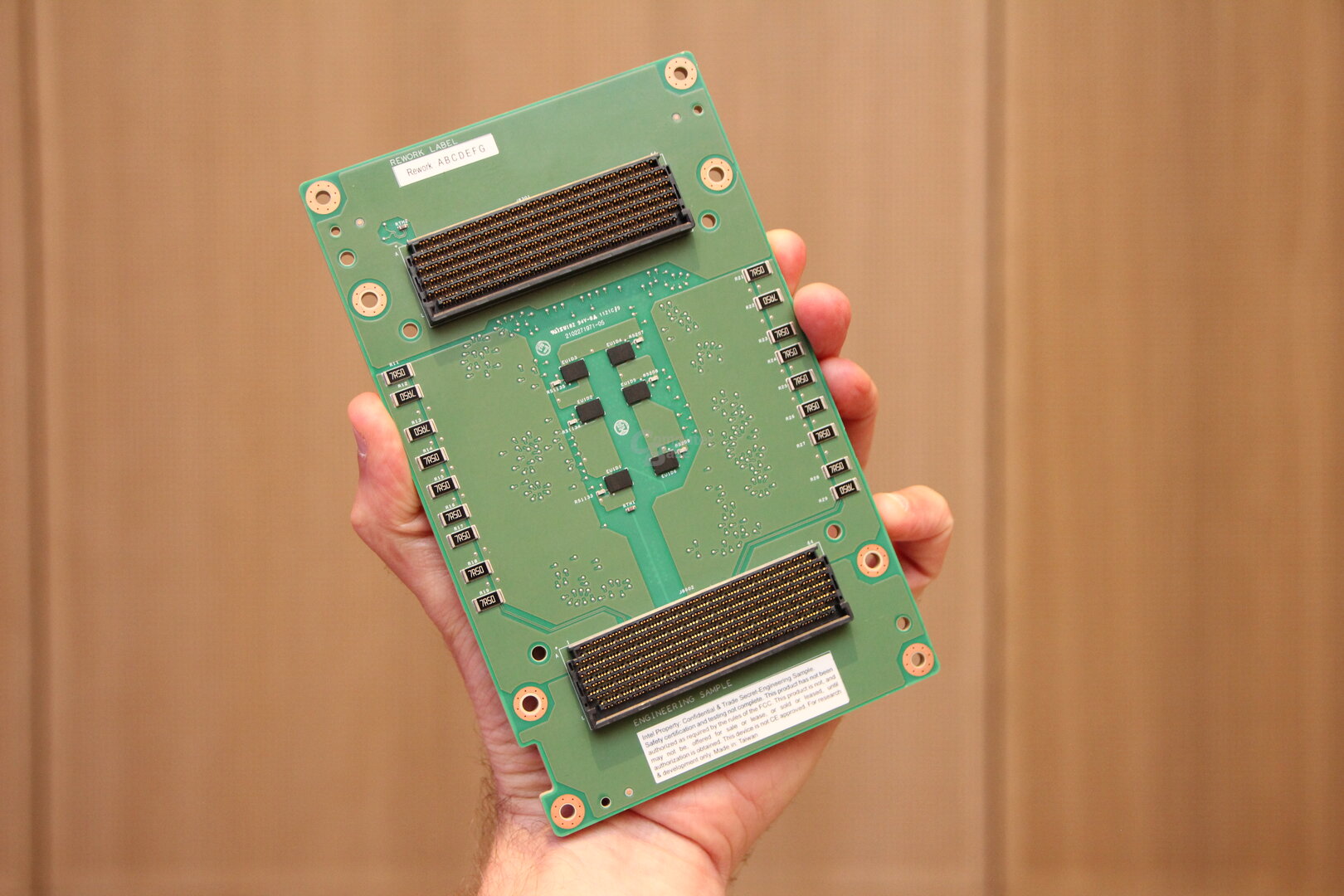

Intel Ponte Vecchio

Intel Ponte Vecchio

Image 1 of 14

Intel Ponte Vecchio

Intel Ponte Vecchio  Intel Ponte Vecchio

Intel Ponte Vecchio  Intel Ponte Vecchio < /figure>

Intel Ponte Vecchio < /figure>

Intel Ponte Vecchio

Intel Ponte Vecchio  Intel Ponte Vecchio

Intel Ponte Vecchio  Intel Ponte Vecchio

Intel Ponte Vecchio  Intel Ponte Vecchio

Intel Ponte Vecchio  Intel Ponte Vecchio < /figure>

Intel Ponte Vecchio < /figure>

Intel SPR and PVC

Intel SPR and PVC  Intel Sapphire Rapids at ISC 2022

Intel Sapphire Rapids at ISC 2022  Intel Sapphire Rapids at ISC 2022

Intel Sapphire Rapids at ISC 2022  Intel Sapphire Rapids at ISC 2022

Intel Sapphire Rapids at ISC 2022  Intel Sapphire Rapids at ISC 2022

Intel Sapphire Rapids at ISC 2022  Intel Sapphire Rapids at ISC 2022

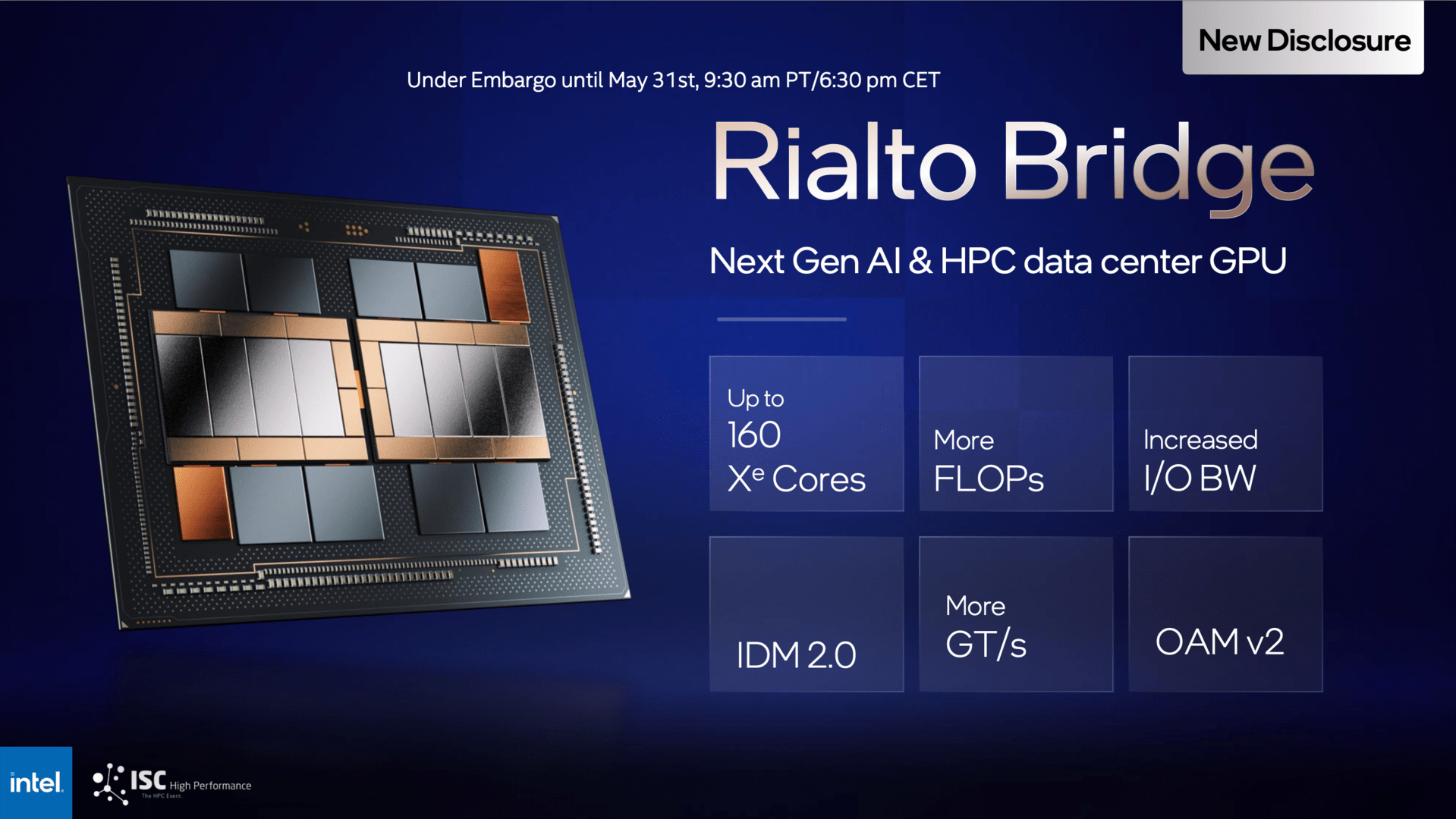

Intel Sapphire Rapids at ISC 2022 Thanks to new technologies in production, Rialto Bridge should provide more power on a similar surface with socket compatibility and thanks to OAM 2.0 support for higher consumption.

The number of Xe graphics cores has been increased from 120 to 160 for this. Intel did not say which generation they belong to, but it will probably stay with the origin. In a press conference, Intel emphasized in advance that Ponte Vecchio was something like the ultimate solution: a maximum number of small chips (tiles) combined in one package.

Rialto Bridge fits into the PVC ecosystem (image: Intel)

Rialto Bridge fits into the PVC ecosystem (image: Intel) Rialto Bridge should find a somewhat more economical way there, because what may be saved in part with the individual chip at Ponte Vecchio is lost again with the extremely complicated package. When asked by ComputerBase whether this means that Rialto Bridge will offer fewer tiles, Intel did not give a clear answer. When asked, not really meant to be taken seriously, whether one could simply count the chips in the image presented, Intel reluctantly said it was just a rendering.

Rialto Bridge (Image: Intel)

Rialto Bridge (Image: Intel) In the end, Rialto Bridge will be the famous optimization of the first product. But that alone should be enough with the expansion of the cores, increased bandwidth and more FLOPs to create a much more rounded product, Intel explained in advance. As part of a keynote, additional details could be given at short notice, ComputerBase will update this message if necessary.

ComputerBase has received information about this article from Intel under NDA. The only requirement was the earliest possible publication date.