Unzählige neue Fabriken zur Chip-Herstellung in vielen Landesteilen Taiwans aber auch in Übersee sind geplant, doch das Packaging als Abschluss-Element für viele Produkte fällt bei ohnehin bereits geringer Menge weiter zurück. TSMC will das nun ändern und sucht neue Standorte.

Im mittleren Südwesten Taiwans soll TSMC nun die besten Chancen sehen, die Stadt Chiayi rückt hierbei in den Fokus, schreibt das taiwanische Branchenblatt Digitimes. Die Infrastruktur ist gut, die Stadt liegt an der High-Speed-Rail-Stammstrecke zur Hauptstadt, auch ein kleiner Flughafen gehört zur Region. Zudem liegt die Stadt zwischen vielen Fabriken und bereits vorhandenen Zentren von TSMC.

Das Packaging ist nicht erst seit ein, zwei Jahren auf den Roadmaps der Foundrys. Denn während das Zweidimensionale schnell an Limits stößt, geht in der dritten Dimension noch einiges mehr – und als Kombination aus beidem richtig viel. Hier hatte TSMC mit SoIC (System on Integrated Chips) vorgelegt, was AMD für Milan-X und in Zukunft auch AMD Ryzen 7 5800X3D nutzt.

Diese Lösungen sind es aber auch, die offenbaren, dass bei weitem nicht genügend Kapazität für solche Modelle zur Verfügung steht. Denn die eigentlich geplanten Lösungen Ryzen 9 5900X3D und 5950X3D sollen laut letzten Informationen nicht mehr erscheinen, Milan-X bekommt den Vorrang, für den Desktop bleibt nur die kleinere Variante mit nur einem CPU-Die.

Neue Packaging-Fabriken bereits im Bau

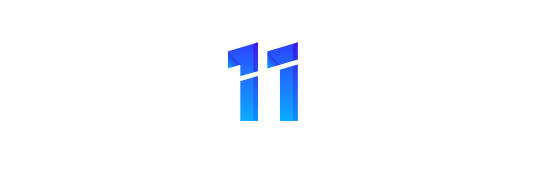

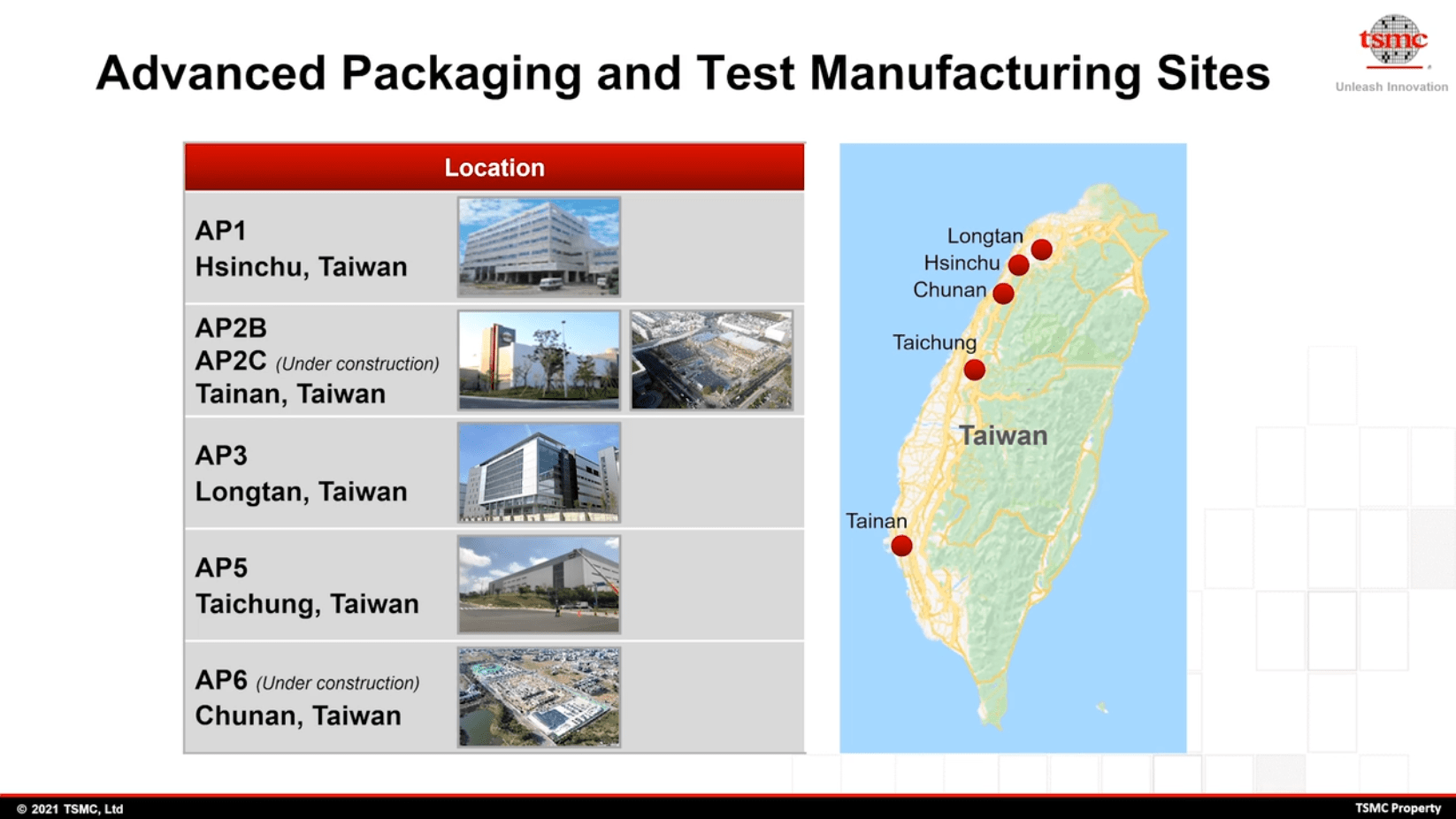

Um der Kundschaft auch in Zukunft genügend fertig gestapelte Chips anbieten zu können, baut TSMC aktuell bereits eine neue riesige Fabrik, die primär für dieses Stacking ausgelegt ist. AP6 heißt der Komplex und soll in drei Phasen mehr Platz bieten als alle bisherigen TSMC-Package/Backend-Zentren zusammen. In diesem Jahr soll die Auftaktproduktion beginnen.

TSMC AP6 in drei Ausbaustufen (Bild: TSMC)

TSMC AP6 in drei Ausbaustufen (Bild: TSMC) Doch für die Zukunft reicht das nicht aus, vor allem, da auch Mitbewerber wie Intel den Fokus in diese Richtung verschieben. Intel erklärte kürzlich, rund 7,1 Milliarden US-Dollar in einen Packaging-Komplex in Malaysia zu investieren.

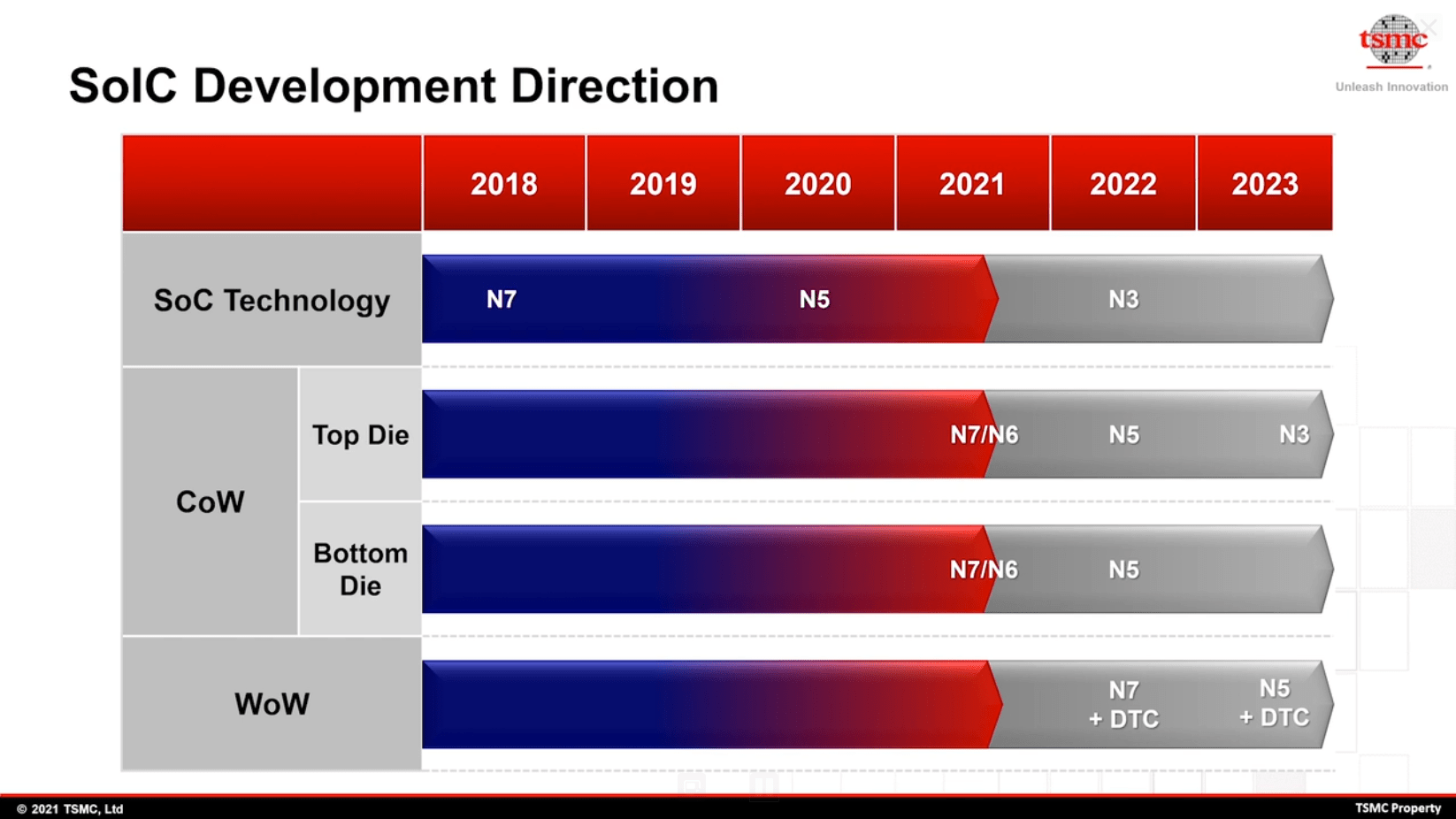

TSMC hatte es bereits selbst dargelegt: In den nächsten Jahren wird das Stacking schneller verfügbar sein, selbst für aktuellste Fertigungsprozesse. Nachdem die ersten Testläufe mit N7 im Markt angekommen sind respektive in Kürze erweitert werden, sollen noch 2022 gestapelte Chips mit N5-Technologie bereit sein, 2023 könnten bereits N3-Lösungen folgen.

SoIC-Roadmap: Der Zeitplan wird schneller (Bild: TSMC)

SoIC-Roadmap: Der Zeitplan wird schneller (Bild: TSMC)