Zuletzt stetig mehr geteasert erklärt SK Hynix nun, dass die Entwicklung von HBM3 abgeschlossen sei. Dieser ist sogar noch einmal etwas schneller geworden, was jedoch auch nötig war, das HBM2e zuletzt die Messlatte nach oben geschoben hatte. Doch bis zum Start dauert es noch.

Stapel mit 16 GByte und 24 GByte parallel

Ursprünglich einmal für das Jahr 2020 bereits im Einsatz geplant, wird es nun frühestens das Jahr 2022, wann die ersten Produkte mit entsprechenden HBM3-Chips ausgestattet werden. Um den Übergang so leicht wie möglich zu machen, werden zum Start auch 16-GByte-Chips aufgelegt, also exakt das, was HBM2e heute auch bietet. Parallel dazu sollen jedoch auch direkt 24 GByte große Stapel verfügbar werden, die so den Einstieg in den nächst größere Kategorie bilden.

Die am besten ausgestattete Profi-Grafikkarte setzt in Form der Nvidia A100 derzeit auf fünf 16-GByte-HBM2e-Chip und bietet dementsprechend 80 GByte VRAM. Der Nachfolger könnte vermutlich spielend die 100-GByte-Marke knacken, wenn er im Jahr 2022/2023 erscheint.

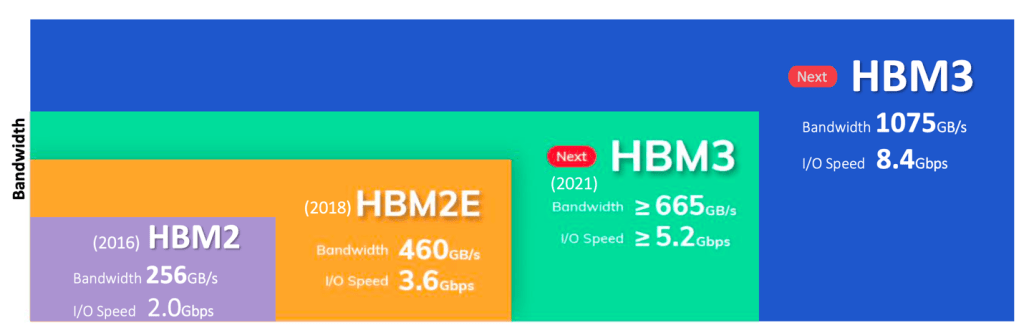

HBM-Entwicklung (Bild: SK Hynix/Rambus)

HBM-Entwicklung (Bild: SK Hynix/Rambus) Bis zu 1.075 GByte pro Sekunde

Der große Vorteil von dem nun finalen HBM3 ist die nochmals gesteigerte Bandbreite, nachdem SK Hynix selbst im Sommer noch von „nur“ 665 GB/s sprach. 819 GByte pro Sekunde will SK Hynix bei diesen Chips zum Start ermöglichen, Rambus hatte zuletzt Controller-Chips spezifiziert, die bis zu 1.075 GB/s bieten sollen. Da weiterhin ein 1.024 Bit-Bus pro Stack genutzt wird wie bisher, kommt die erhöhte Bandbreite durch den höheren Takt zustande.

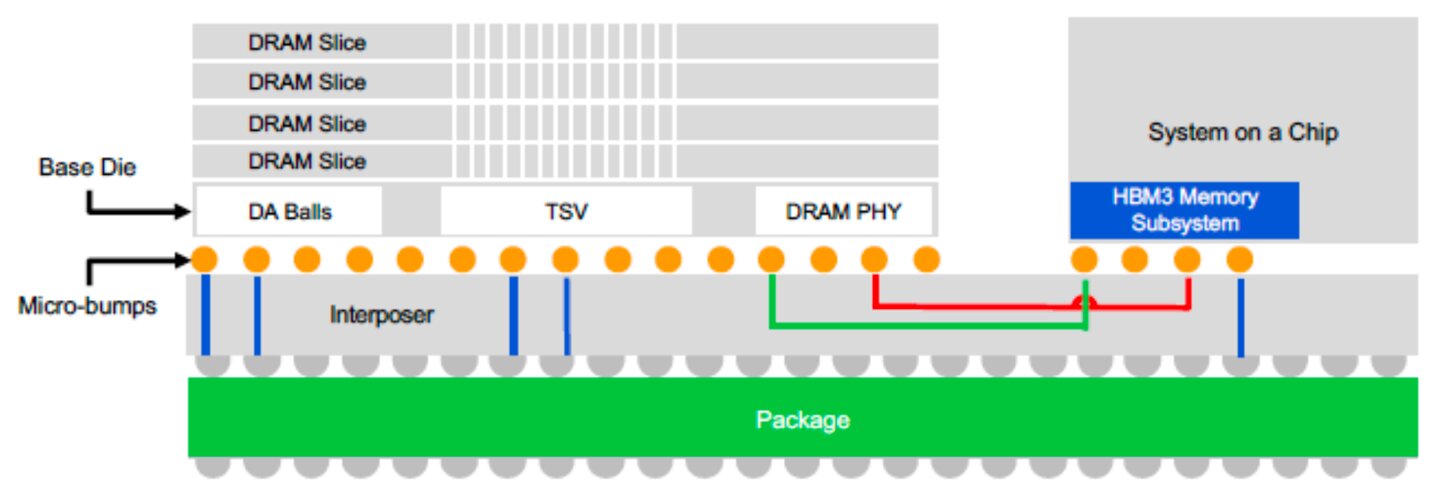

HBM3 im internen Aufbau (Bild: Rambus)

HBM3 im internen Aufbau (Bild: Rambus) HBM3 steht eben erst am Anfang seines Lebenszyklus. Das gilt auch für die Kapazität: Auch hier wurde bereits der Grundstein für 64-GByte-Chips gelegt, dann muss jedoch jede der Lagen deutlich mehr Kapazität bieten. Denn der neue Chip mit 24 GByte besteht intern schon aus 12 Layern, die mit TSVs durchkontaktiert sind. Heraus kommt am Ende auch nicht mehr das charakteristische längliche Speicher-Chip-Design, der Neuling ist nun quadratisch.

SK Hynix HBM3 (Bild: SK Hynix)

SK Hynix HBM3 (Bild: SK Hynix) Segen des JEDEC-Konsortium steht noch aus

Was immer noch fehlt, ist die offizielle Absegnung durch das Speicherkonsortium JEDEC. Diese rennen aber hier und da neuen Standards öfter hinterher, Speicherhersteller müssen die Entwicklung selbst vorantreiben, sodass diese letztlich zum Standard werden. In den meisten Fällen klappt das auch, denn ganz allein und ohne erste begleitende Schritte wird auch das nicht vollzogen. Das dürfte aber nun in Kürze folgen, denn auch Synopsys hat mit seinen Partnern Micron, Samsung und SK Hynix kürzlich die Zusammenarbeit und Zertifizierung der Tools und Controller für HBM3 mit 921 GB/s Bandbreite bekannt gegeben.