As part of the Hot Chips 33, Intel spoke about its packaging technologies for upcoming 2D designs and 3D stacks and chip sets. In the live stream, Ravi Mahajan and Sandeep Sane spoke in particular of the flexibility made possible by Co-EMIB, Foveros and ODI as well as Silicon Interposer.

As at SemiCon West 2019 and CES 2019 and most recently at Intel Foundry IDM 2.0, Intel spoke at Hot Chips 33 about new packaging technologies that Intel and TSMC have recognized as a great opportunity for the future. On the basis of EMIB and Foveros, Intel wants to be able to implement significantly more complex designs with up to 36 chip sets with Co-EMIB. This should create the basic requirements for a heterogeneous integration (HI) of future chips.

In addition, Co-EMIB, also known as EMIB-Foveros, the chip design with several layers also make it more flexible. The so-called 3D stacking of chips with different functions should make completely new products possible.

Technology Provider: Intel packaging technologies for chiplets and 3D (Image: Intel)

Technology Provider: Intel packaging technologies for chiplets and 3D (Image: Intel)  Technology Provider: Intel packaging technologies for chiplets and 3D (Image: Intel)

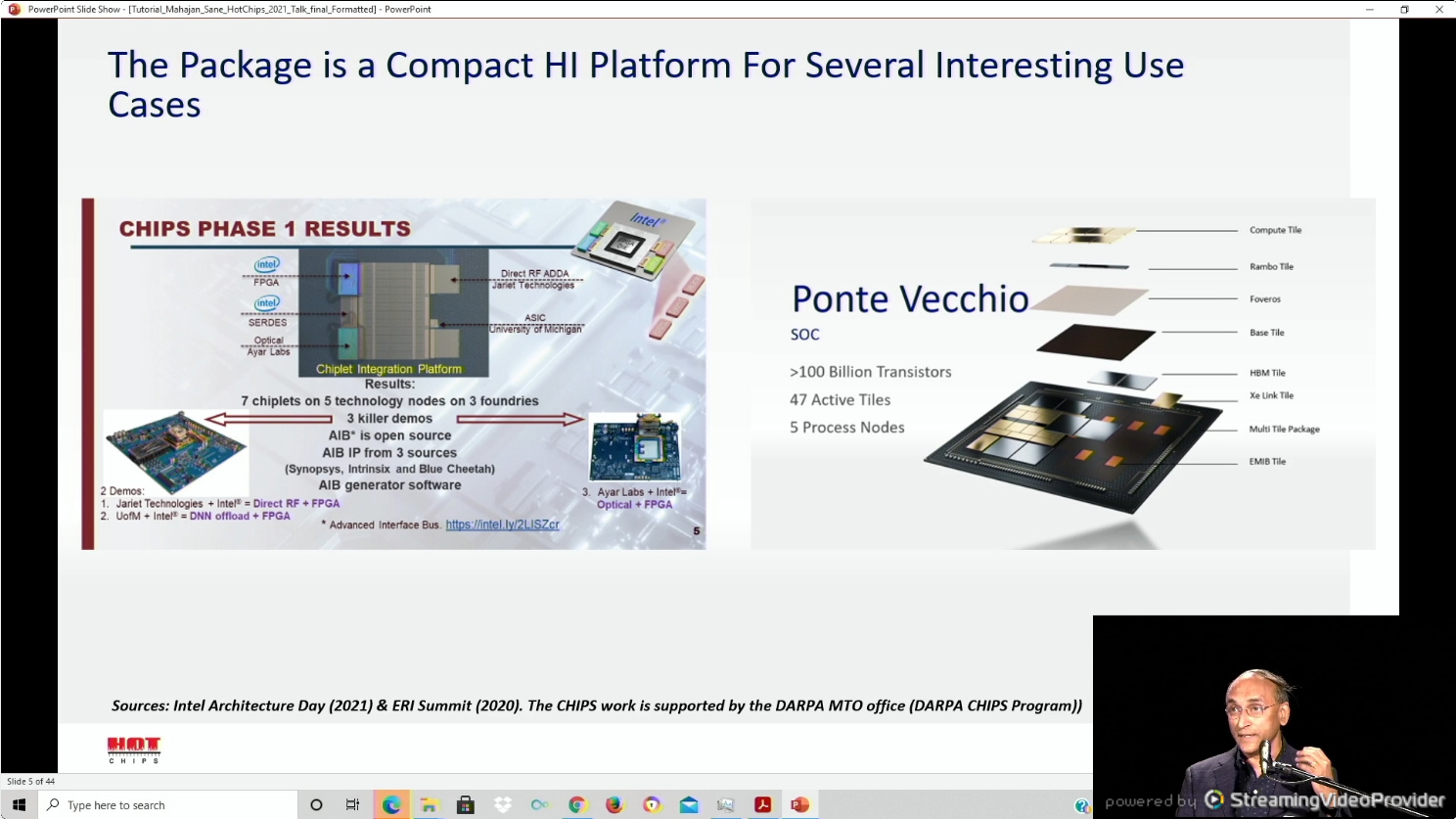

Technology Provider: Intel packaging technologies for chiplets and 3D (Image: Intel) Using the example of the powerful HPC graphics solution Ponte Vecchio, Intel once again demonstrated how broad the field of use cases for highly integrated chips is. Ponte Vecchio is a real monster SoC with eleven EMIB connection elements, 47 active tiles and 5 process nodes, some of which do not come from in-house but from TSMC. Intel also highlighted the mix of manufacturing processes from different manufacturers and wants to show its flexibility, not just being dependent on one manufacturer, but primarily on itself so far.

Apart from the areas of application “Graphics, Client and FPGA” and background information intended by Intel for the new 2D and 3D packaging, there was little new and no completely new products with these technologies at the start of the Hot Chips 33. However, this may change during the semiconductors industry conference, starting today the presentations of CPU architectures, for example.

Before that, Intel had already had a glimpse of Sapphire Rapids in With regard to its packaging with ten to fourteen EMIB connection elements.

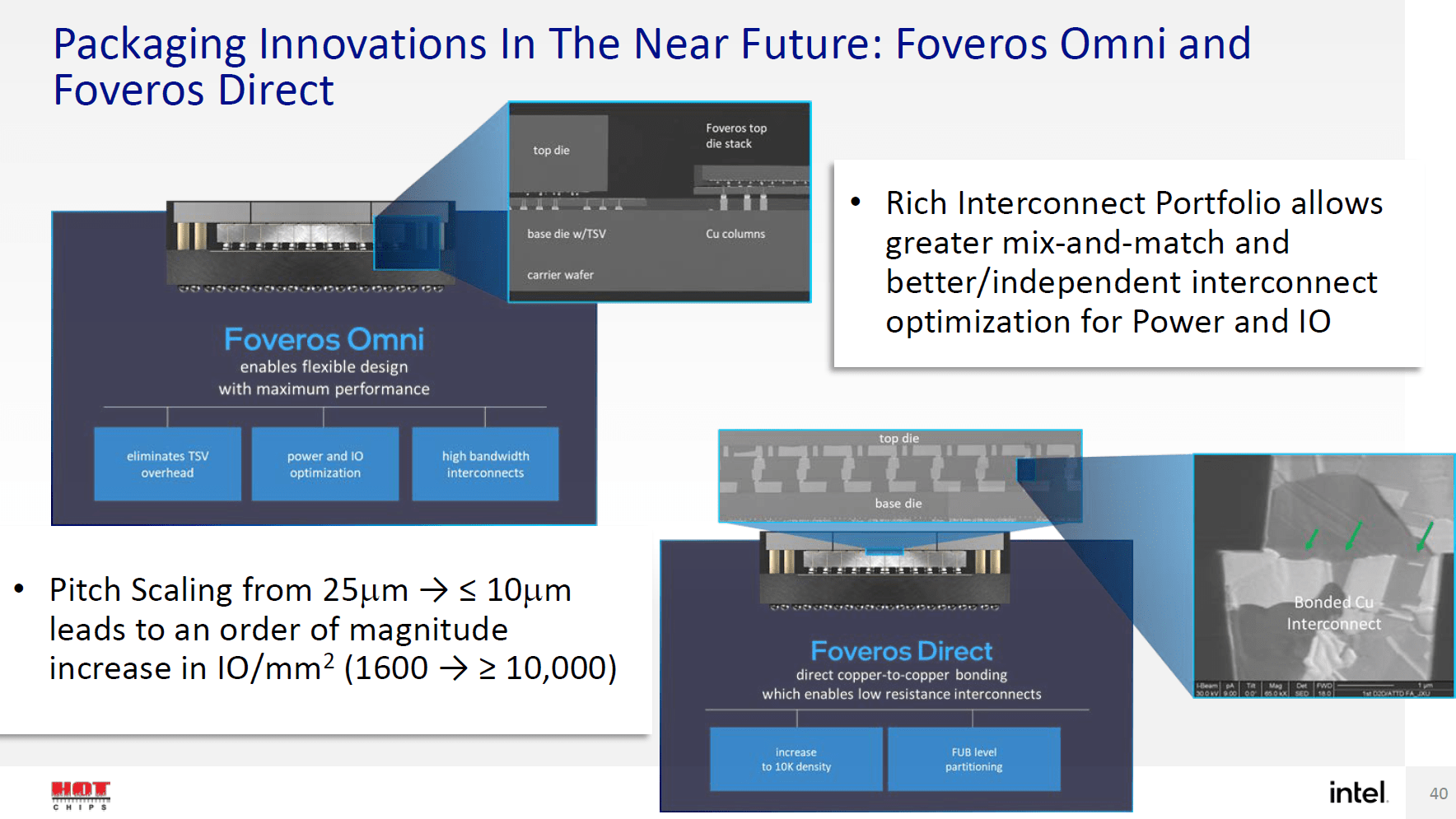

AMD spoke to Hot Chips 33 about its stacking technology in cooperation with TSMC, which will be available with the upcoming Ryzen and additional L3 Cache, the so-called 3D V-Cache, which is up to 192 MB in size, is used for the first time. Intel will not offer a similar technology until 2023, with Foveros Direct.

Next Gen Intel Foveros (Image: Intel)

Next Gen Intel Foveros (Image: Intel)