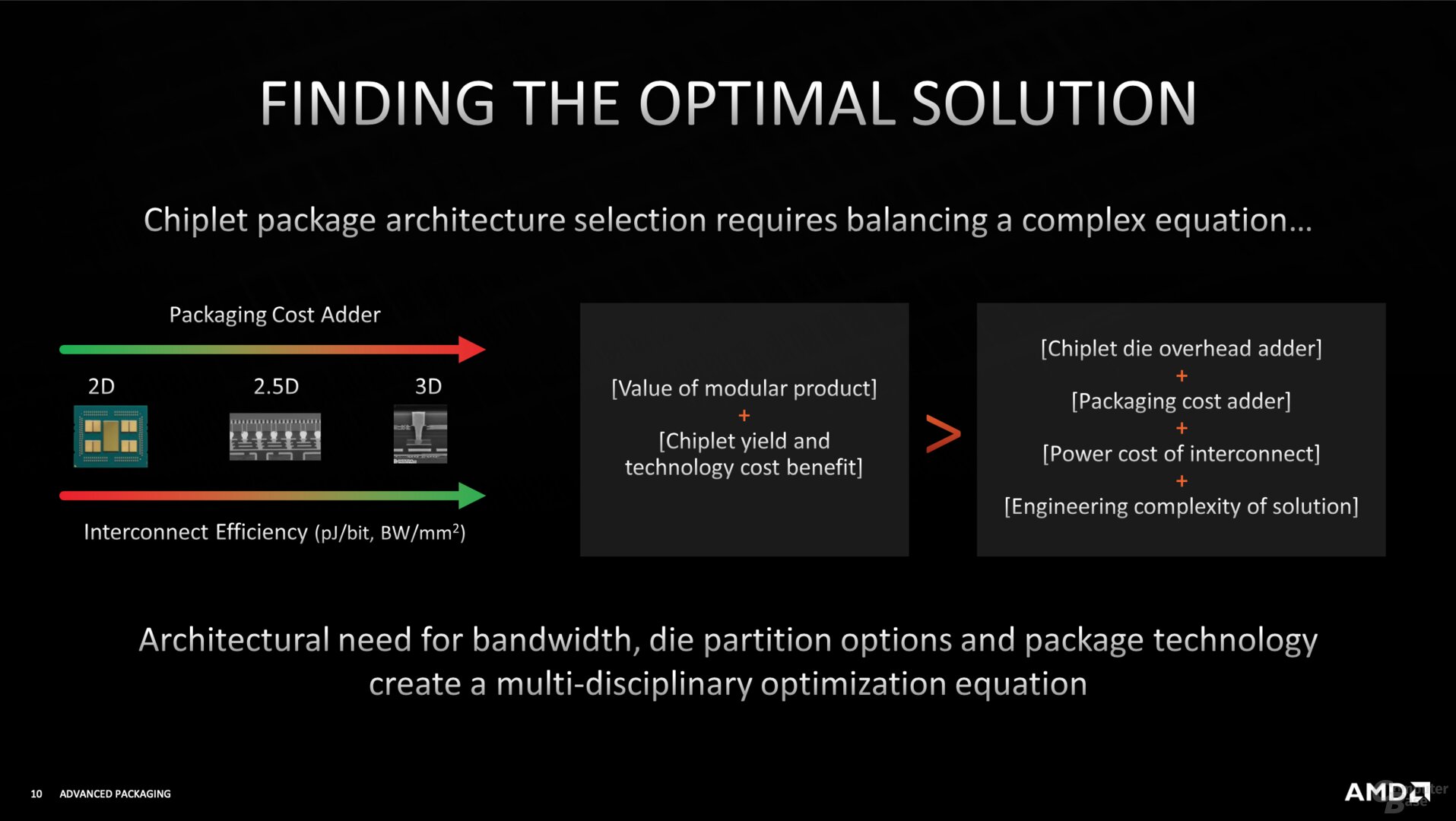

For Hot Chips 33, AMD gave further insights into its stacking technology, which will be used for the first time with the upcoming Ryzen and the additional L3 cache. AMD makes it clear that the variety of solutions currently being developed will shape the future of chips in industry. It is important to choose the right one.

Not every solution is suitable for everyone, explains Raja Swaminathan, Senior Fellow at AMD for packaging right at the start. But without a doubt, the future belongs to the modular design and the matching and coordinated package in order to continue Moore’s Law. The industry has understood this, a variety of solutions from well-known manufacturers demonstrate this.

All manufacturers have to keep an eye on economic efficiency, AMD calls it PPAC (power, performance, area and cost). The thought-out path must then be chosen via these points, because not everything fits into the cheap mainstream market, for example, the costs would simply be too high. For example, AMD will offer the first solution with 3D stacking in the upper segment, the manufacturer suggests at least a twelve-core processor, and the 16-core processor should also be available with an additional L3 cache.

AMDs 3D-Stacking

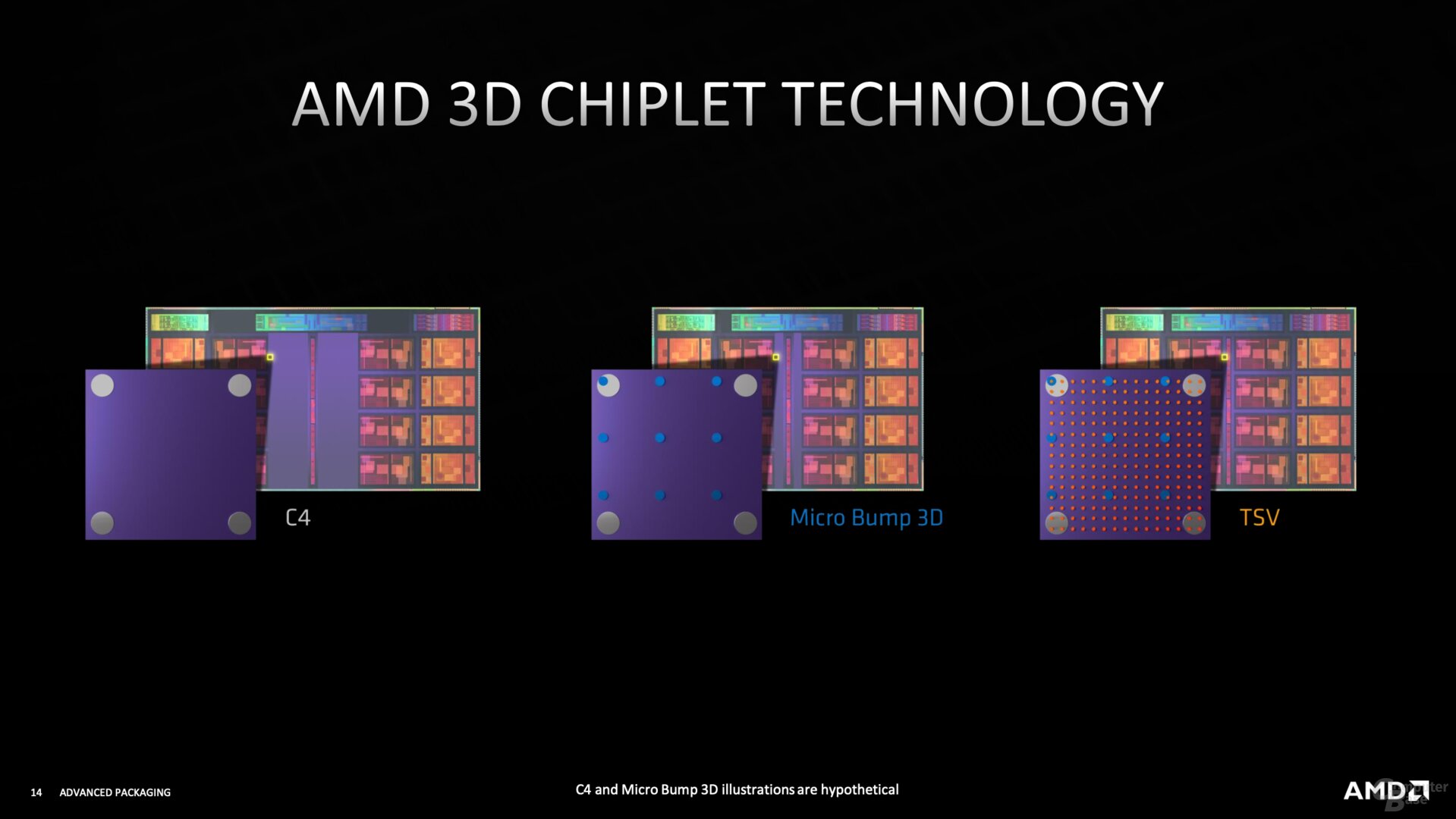

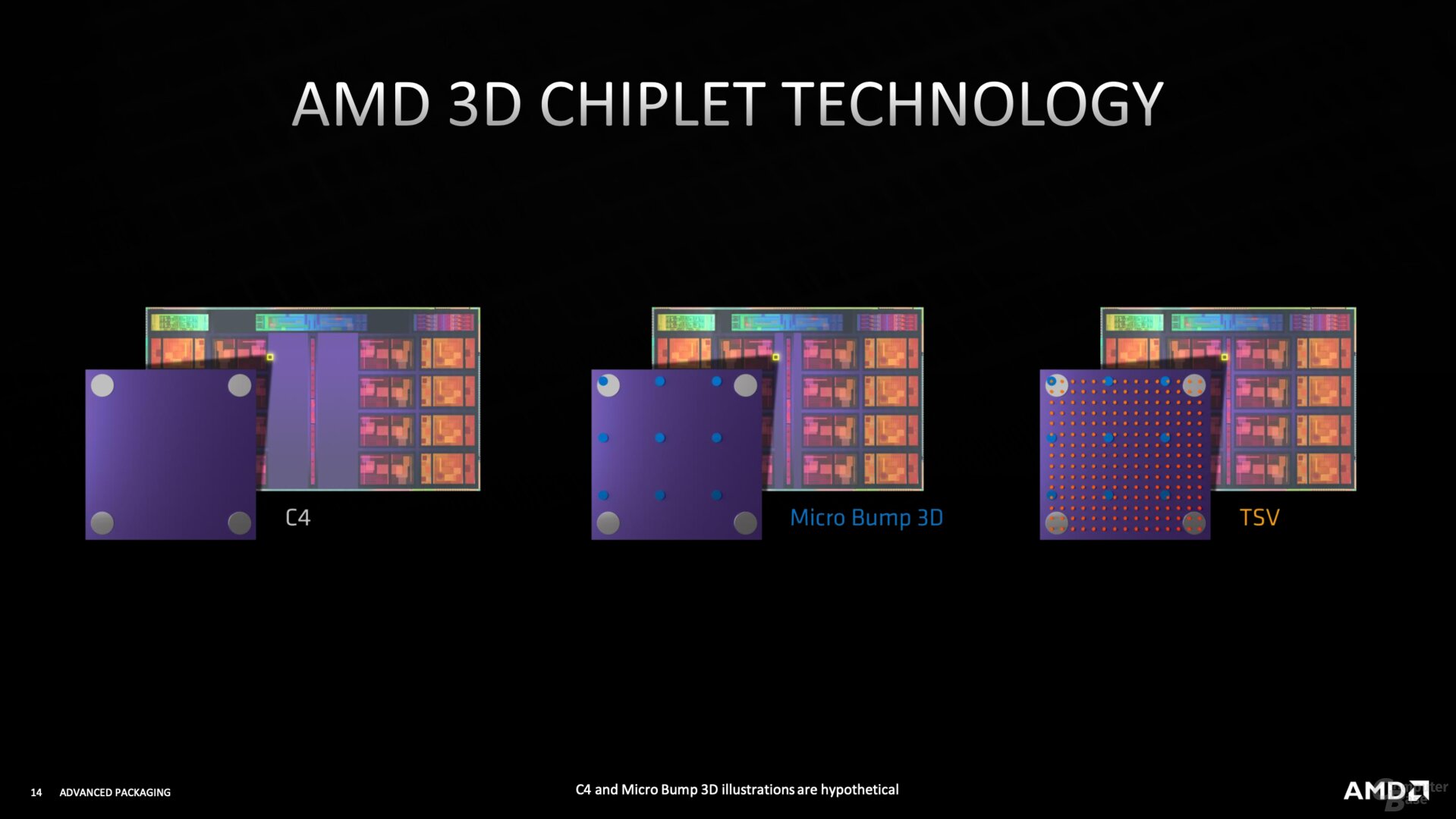

AMDs 3D-Stacking At the unveiling of the 3D V-Cache in June, AMD had already announced that the previous Ryzen 5000s were already prepared for stacking with regard to the CPU die. There are small elements on the die for this, the chip bonding takes place via direct contact between the copper layers, no additional BGA contact surfaces or the like are required.

Today we can now show in detail what they look like: Extremely small and with the smallest distance of 9 µm between the contacts, they should have extremely high signal quality with low power consumption and, above all, offer a clear advantage over classic microbumps. With this, AMD, together with TSMC's current technology, would clearly beat Intel on paper, the future Foveros Direct will have gaps of “<10 µm" - but it will not come until 2023.

-

AMDs 3D-Stacking

AMDs 3D-Stacking

Image 1 of 4

AMD's 3D-Stacking

AMD's 3D-Stacking  AMDs 3D-Stacking

AMDs 3D-Stacking  img src = “/wp-content/uploads/990294d3bddd29fff5c7fdd8eb81ffb9.jpg” /> AMD's 3D-Stacking

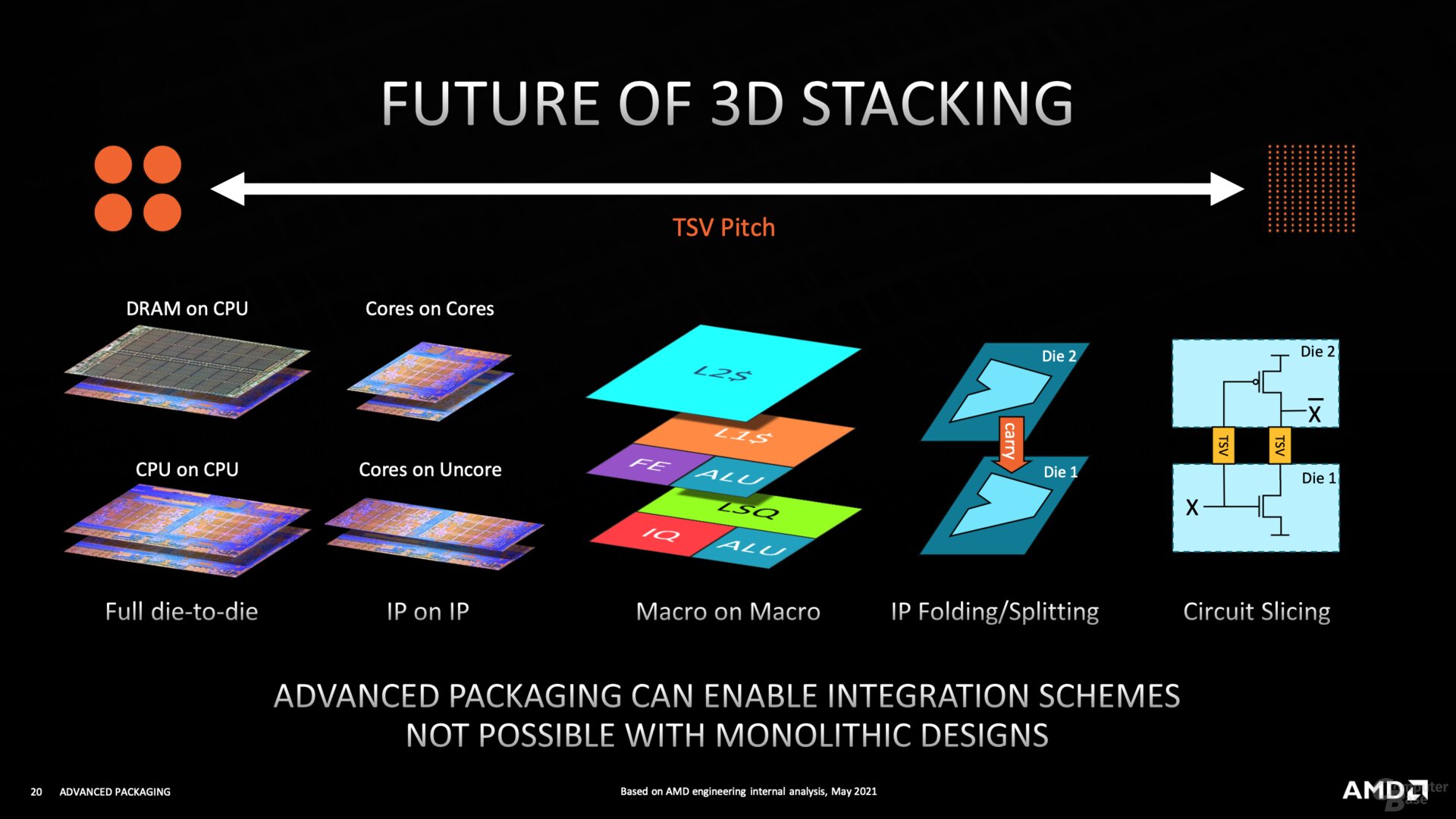

img src = “/wp-content/uploads/990294d3bddd29fff5c7fdd8eb81ffb9.jpg” /> AMD's 3D-Stacking The future will continue to develop in this direction, According to AMD, the possibilities are almost endless. Costs and benefits as well as the chosen market should ultimately decide on an implementation.

The future has a variety of solutions ready

The future has a variety of solutions ready