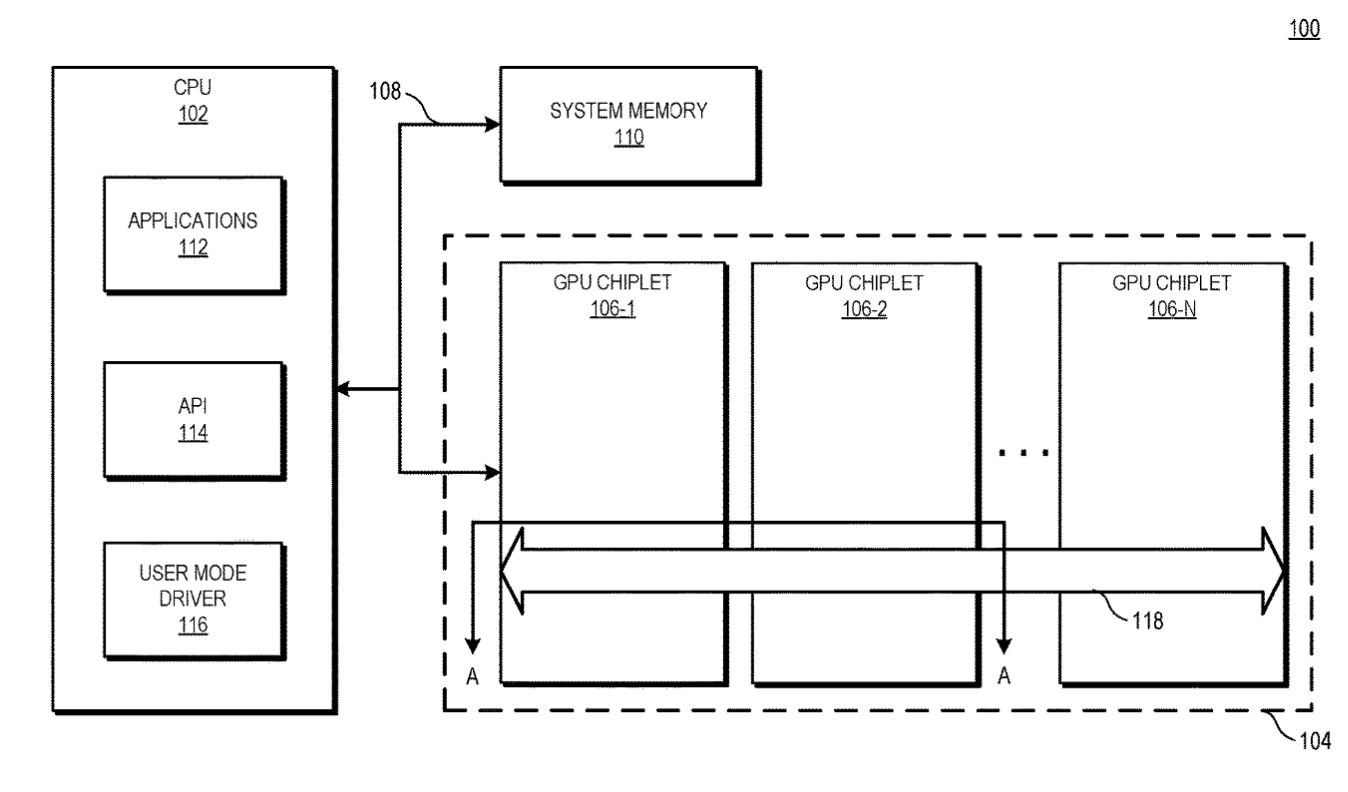

Zwei neue Patente von AMD, ein mögliches Chiplet-Design von GPUs betreffend, bringen eine „Active Bridge“ und den Cache ins Spiel. Über einen für jedes Chiplet kohärenten L3-Cache sollen Daten bei Bedarf ausgetauscht werden können, während ein primäres Chiplet dabei die Organisation und Kommunikation übernehmen soll.

Ein flexibles Chiplet-Design für GPUs

Unter der Patentnummer „US 2021/0097013 A1“ hat AMD ein neues Patent mit dem Titel „Active Bridge Chiplet with integrated Cache (PDF)“ für zukünftig potenziell mögliche Grafikprozessoren im Chiplet-Design veröffentlicht.

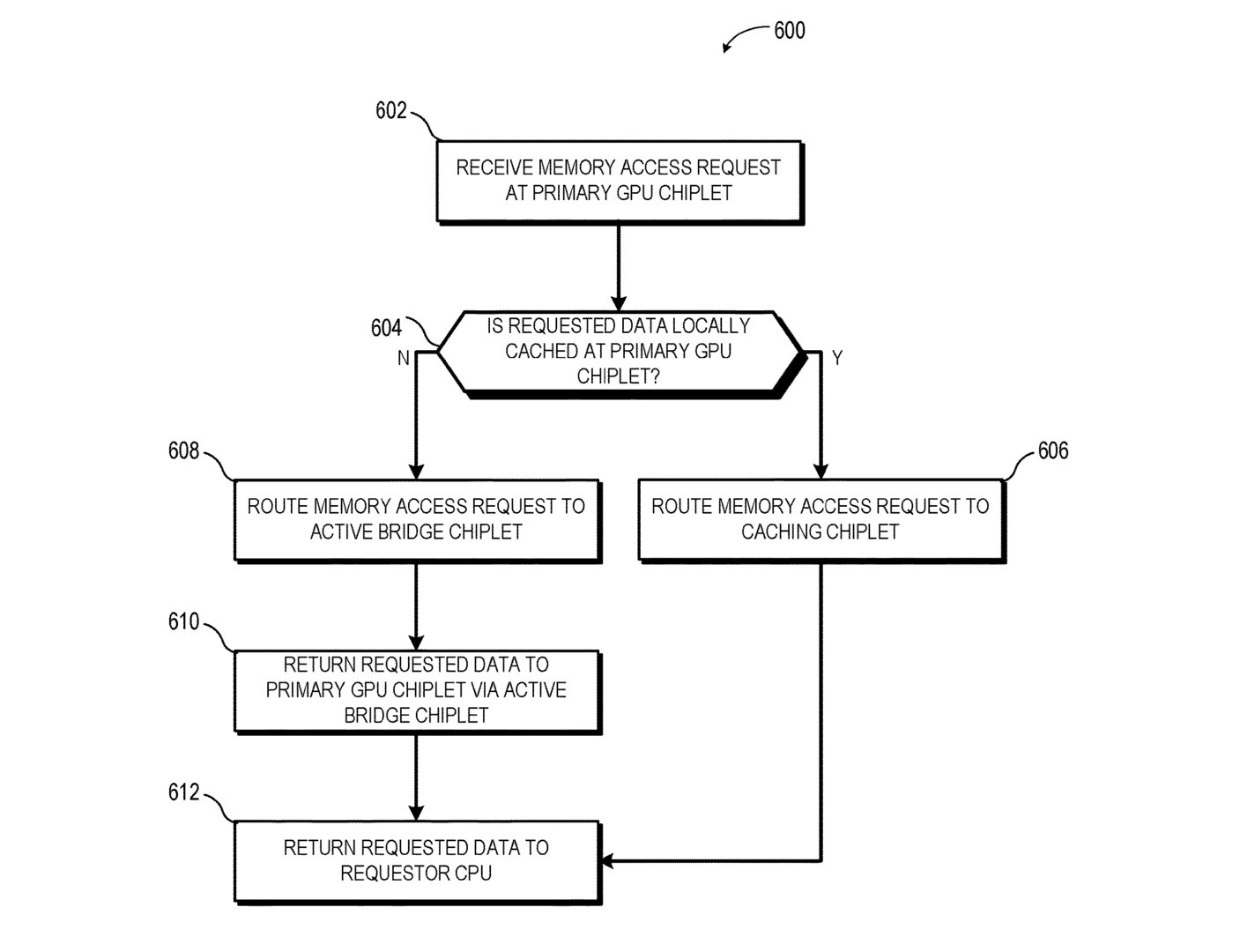

US 2021/0097013 A1: Active Bridge Chiplet with integrated Cache (Bild: AMD)

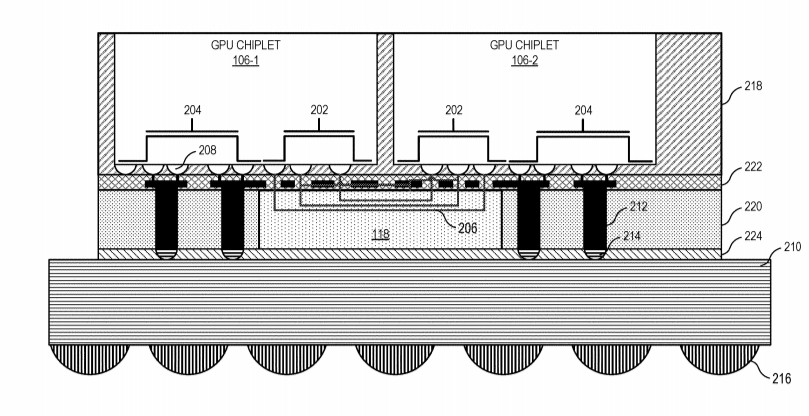

US 2021/0097013 A1: Active Bridge Chiplet with integrated Cache (Bild: AMD) Neben einer sogenannten „Active Bridge“, einen aktiven Silizium-Die, der die Verbindung unter den GPU-Chiplets übernimmt, wird einmal mehr ein über alle Chiplets kohärenter L3-Cache sowie ein „Primary Chiplet“ beschrieben, wodurch Programme die GPU auch weiterhin als eine Einheit wahrnehmen.

In dem Patent „GPU Chiplets using High Bandwidth Crosslink“ aus dem Dezember 2019 wurden stattdessen noch die passiven HBX-Verbindungen in Form eines Interposers („Crosslinks“) mit sehr hoher Bandbreite beschrieben.

Der Cache wandert auf die Brücke

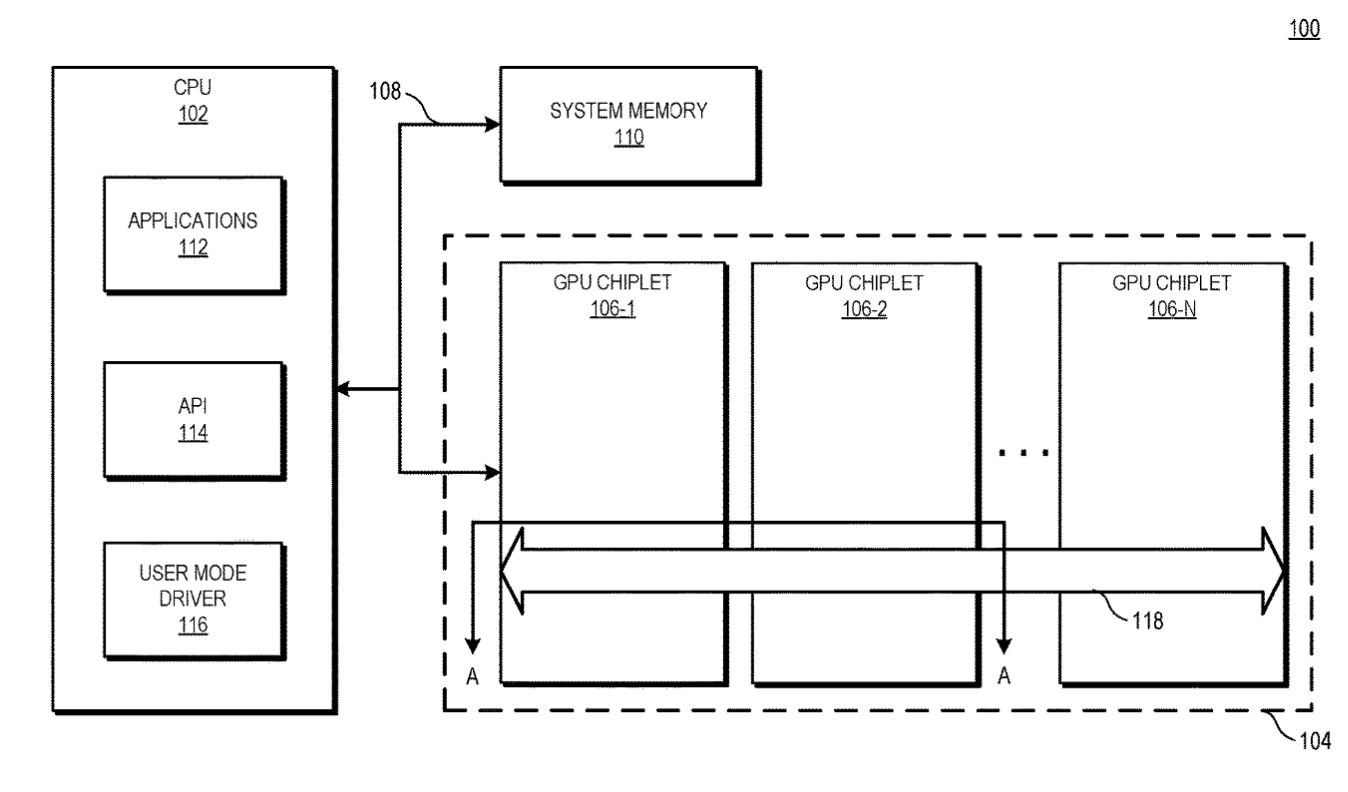

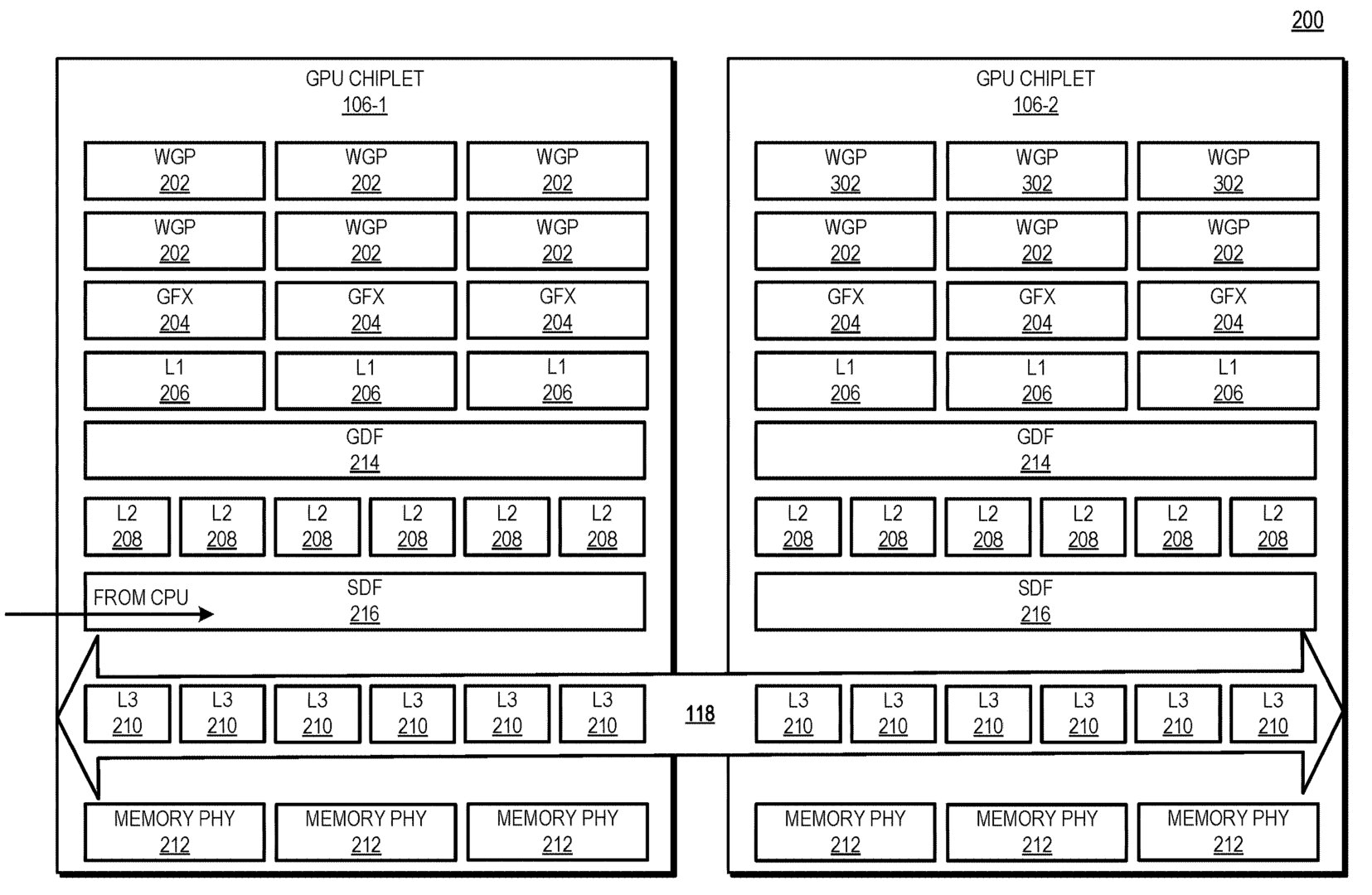

Die Besonderheit der „Active Bridge“ besteht darin, dass der L3-Speicher direkt auf der Brückenverbindung und nicht mehr auf dem entsprechenden GPU-Chiplet untergebracht werden soll. Das erklärt auch die aktive Auslegung der Brücke.

Zudem ist die Größe des L3-Cache damit durch die Größe der „Active Bridge“ beliebig skalierbar und ermöglicht Lösungen für Systeme respektive GPUs und Beschleunigern mit wenigen (1 bis 2) oder vielen (3 und mehr) GPU-Chiplets.

Der L3-Cache ist damit auch von der Hitzeentwicklung und dem Stromverbrauch der GPU-Chiplets entkoppelt. Ob der Cache damit tatsächlich besser gekühlt werden kann oder einfach die dezentrale Hitzeentwicklung von Vorteil ist, geht aus der Patentschrift indes nicht hervor.

-

US 2021/0097013 A1: Active Bridge Chiplet with integrated Cache (Bild: AMD)

Bild 1 von 3

US 2021/0097013 A1: Active Bridge Chiplet with integrated Cache

US 2021/0097013 A1: Active Bridge Chiplet with integrated Cache

US 2021/0097013 A1: Active Bridge Chiplet with integrated Cache

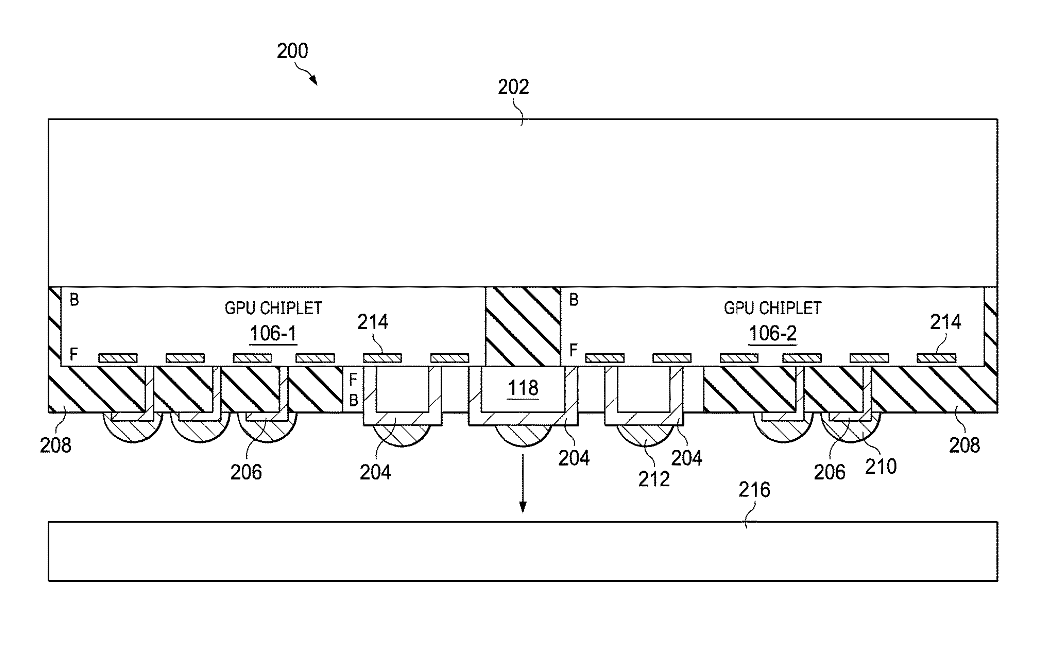

Die Anbindung an den VRAM ist nach wie vor auf dem GPU-Chiplet und nicht auf der „Active Bridge“ untergebracht, während die Verbindung zwischen Brücke und Chiplet über TSVs („Through Silicon Vias“) erfolgt, die durch das Chiplet laufen. Die Brücke selbst besitzt keine Vias, nur Strukturen und Leiterbahnen auf der Oberseite.

Die Fertigungsmethoden für die Active Bridge

Ein ebenfalls auf FreePatentsOnline veröffentlichtes neues Patent vom 1. März beschreibt unter dem Titel „Fabricating Active-Bridge-Coupled GPU Chiplets (PDF)“ sowie der US-Patentnummer „US 2021/0098419 A1“ die Fertigungsmethoden der neue „Active Bridge“ und deren Anbindung an die GPU-Chiplets.

US 2021/0098419 A1: Fabricating Active-Bridge-Coupled GPU Chiplets (Bild: AMD)

US 2021/0098419 A1: Fabricating Active-Bridge-Coupled GPU Chiplets (Bild: AMD) Die GPU-Chiplets werden auf einen Träger-Wafer befestigt und dann gemeinsam mit dem Active-Bridge-Die verbunden. Das Patent unterscheidet im Wesentlichen nur zwischen Face-to-Face-Verbindungen und Face-to-Back-Verbindungen.

Noch Zukunftsmusik

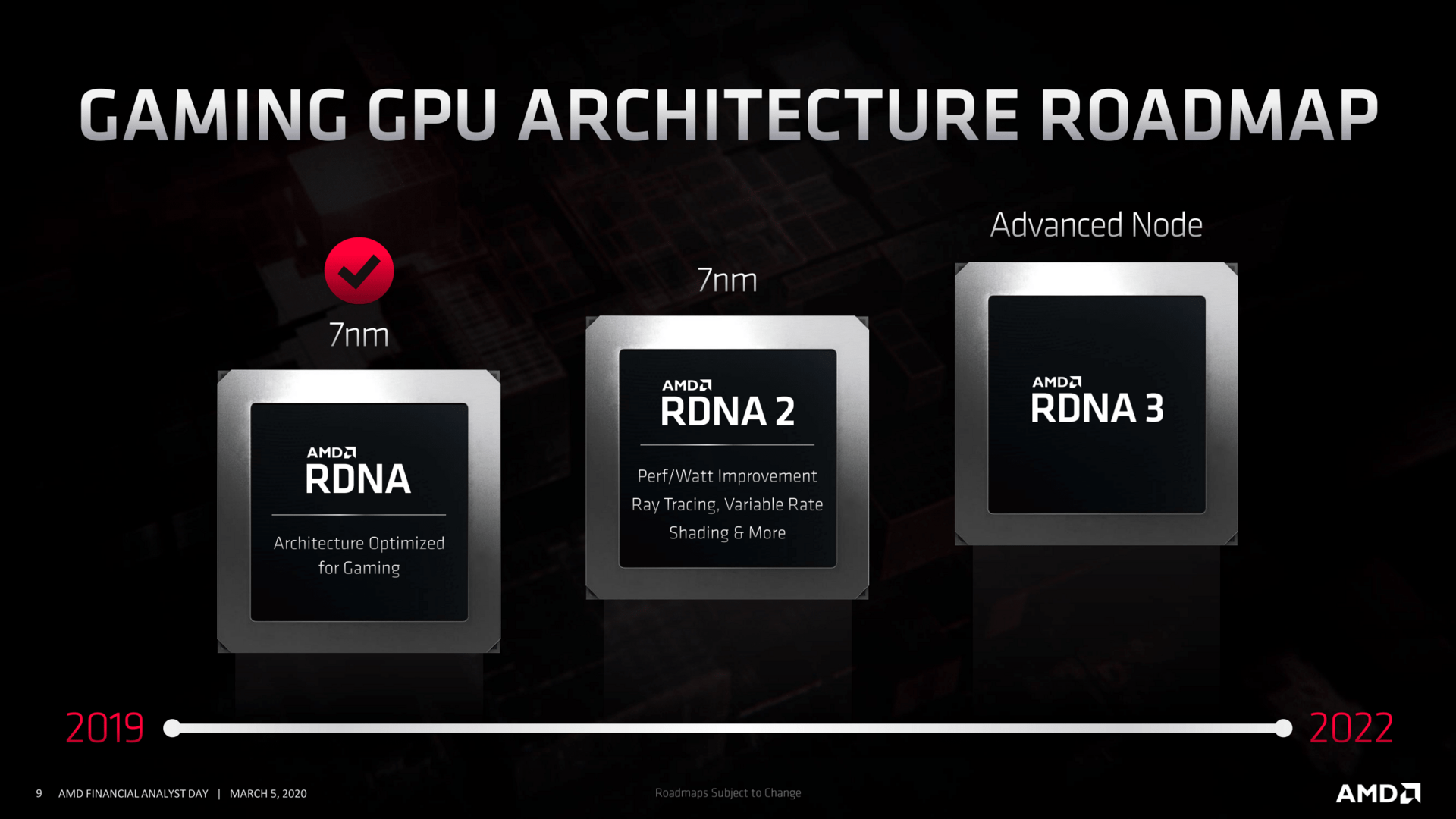

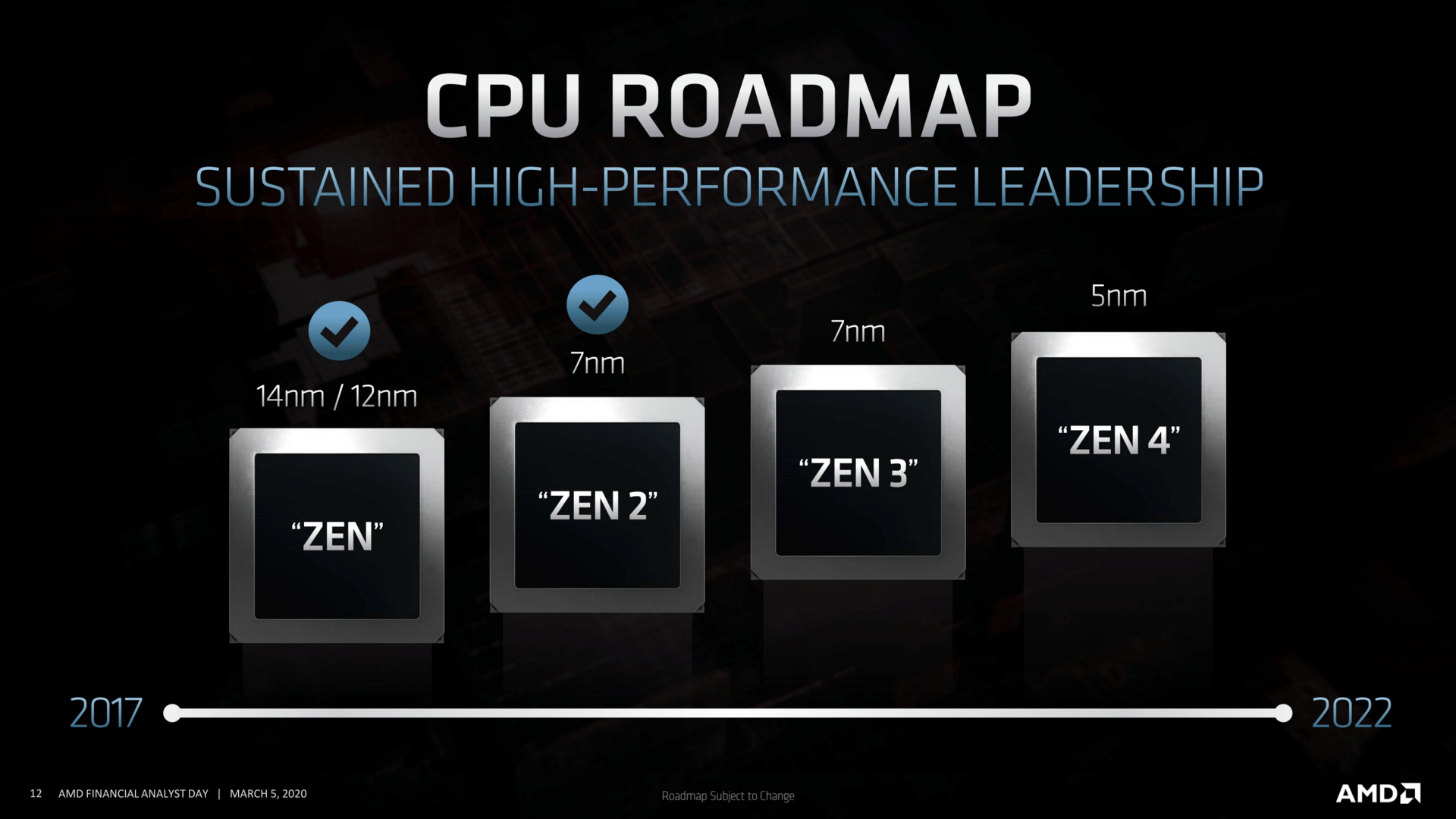

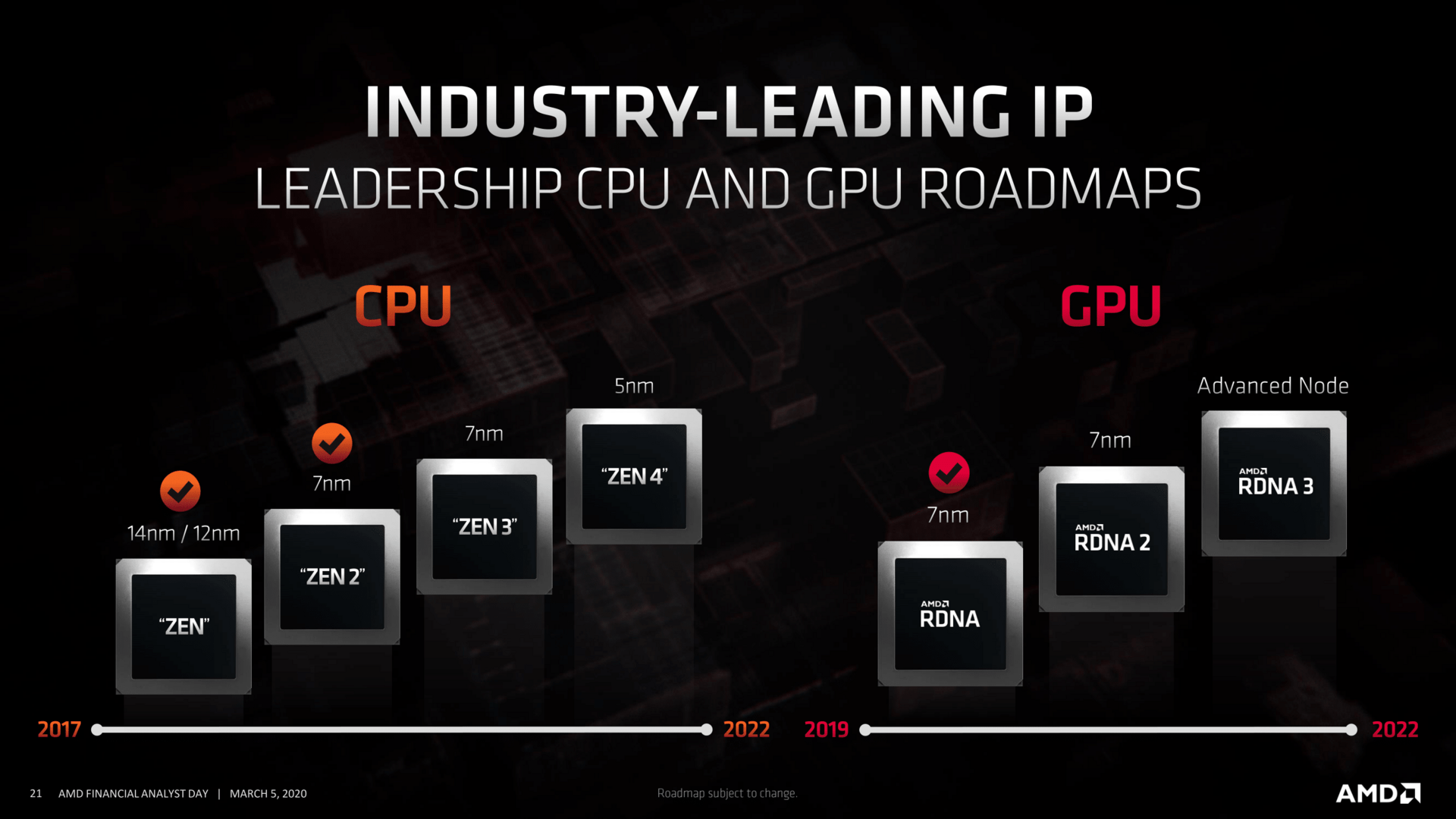

In der Vergangenheit wurden mehrfach Gerüchte laut, RDNA 3 oder RDNA 3+ könnten auf ein solches Chiplet-Design setzen, vermutlich aber eventuell eher ein Nachfolger der professionellen Lösung CDNA. Zen 4 und RDNA 3 sind aber noch Zukunftsmusik und sollen voraussichtlich Ende 2022 erscheinen.

-

AMD Roadmap (Bild: AMD)

Bild 1 von 3

AMD Roadmap

AMD Roadmap

AMD Roadmap

AMD selbst hat sich bislang nicht offiziell zu einem Multi-Chip-Design und dem Ansatz der GPU-Chiplets für kommende Gaming-GPUs der Serie Radeon geäußert.

Die Redaktion dankt Community-Mitglied „ETI1120“ für den Hinweis zu dieser Meldung und „Colindo“ für die tatkräftige Unterstützung beim Studium der Patente sowie der Umsetzung.